FPGA Development Tools

QuickLogic provides a complete design environment for Field Programmable Gate Array (FPGA) designs. QuickLogic development software helps you increase productivity, shorten design cycles, achieve design performance and power requirements quickly and efficiently. QuickLogic provides tools to guide you from concept to silicon.

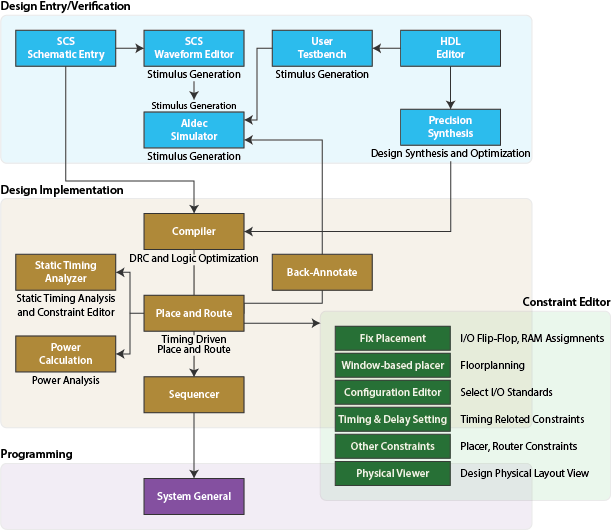

QuickWorks® supports Windows operating systems, and provides a comprehensive design environment ranging from schematic and HDL-base design entry, HDL language editors and tutorials, logic synthesis, place and route, timing analysis, and simulation support. QuickLogic has partnered with Mentor Graphics and Aldec Inc. to provide industry leading synthesis and simulation tools, as well as provide an interface to other industry standard EDA tools.

In addition, QuickLogic provides various reference design kits and software development kits to shorten your verification cycles.

Design Flow

Please read the software license agreement.

| Name | Version | Size | Updated | Notes |

|

Latest QuickWorks for SRAM FPGA |

Contact support@quicklogic.com |

|||

|

QuickWorks2010.4.1 |

Version PolarPro2, PolarPro, Eclipse II and Eclipse I |

|||

|

QuickWorks 9.7.4 |

Supports QuickRAM, pASIC3 and EOL pASIC1 and pASIC2 families. |

|||

| 2010.4.1 | 207 MB | January 19, 2011 |

This version doesn’t include Mentor Graphics Precision Synthesis. Please download Mentor Graphics Precision Synthesis and Synthesis Library separately. |

|

|

license.dat for v9.7.4 (Right click the link to save the file) |

9.7.4 | 301.4 MB | February 5, 2008 |

For EOL devices. Please make sure you don’t have any other QuickWorks versions installed on your system. License installation instructions: Please copy the license.date license file to the data directory of your SpDE installation. The default installation directory path is C:\pasic\spde\data\license.dat. |

| 1.35a | 4.9 MB | June 9, 2015 |

QL9600 Software for System General Programmers |

|

| 9.4.1 RC3 | 64 MB | |

||

| Download from www.mentor.com |