# Wake-Up and Verify (WAV) Data Sheet

# ••••• Proven System Block (PSB) for QuickLogic Customer Specific Standard Products (CSSPs)

### **Features**

The QuickLogic WAV PSB has the following features:

- Allows for detection of changes of state of external devices (keyboards, headphones, etc.) and internal devices (sliders) while the CPU is in a power-down state

- CPU remains in a low power state during detection, greatly reducing system-level power consumption

### **Overview**

System architects must constantly balance the requirements for system performance against system power. This is often a fine balance, which becomes more complicated when the system must manage external devices connecting into the architecture at random and infrequent periods. Devices such as external keyboards, headphone jacks, and computers are typical features consumers connect to their mobile devices to extend functionality. The issue facing designers is how they can detect these activities while making sure minimal power is consumed waiting for this activity. This system requirement is not restricted to external devices, but also for internal connectivity within a mobile device. This includes functionality typically involving the CPU such as detection of slider motion, keypad or touch press and sensor activities.

QuickLogic has developed a new PSB which enables detection of activities on a bus or signal while the system is in a power down state. This implementation can consume fewer than 5  $\mu$ A of current while it monitors activities and detects when to wake up the system or part of the system to act upon. When this PSB is used in conjunction with other PSBs to build a CSSP, the solution can be used to detect, act upon and inform various aspects of the system - enabling a more efficient solution for the management of active and standby power during specific application tasks, resulting in much longer battery life.

The WAV PSB is available for inclusion in QuickLogic CSSPs using the ArcticLink<sup>®</sup>, ArcticLink II, PolarPro<sup>®</sup> and PolarPro II solution platforms.

# **PSB** Architecture

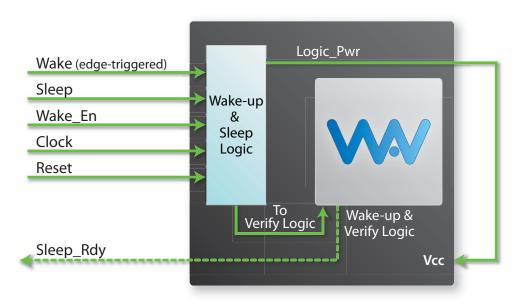

### Wake-Up and Sleep Logic

The Wake-Up and Sleep Logic contains the necessary logic to put the CSSP into sleep mode or to wake up the CSSP from Sleep mode.

The CSSP enters Sleep mode when the external *Sleep* signal is set high. To bring the CSSP out of Sleep mode, the *Sleep* signal must be reset to low and the *Wake\_En* signal must be set high. Once these conditions are met and the CSSP detects a rising-edge *Wake* signal, the *Logic\_Pwr* pin will be set to 1.8 V, which turns on the logic voltage (Vcc).

### Wake-Up Verify Logic (Optional)

The Wake-Up and Verify Logic is optional but recommended when coming out of Sleep mode. Although the module must be tailored for the application, the basic implementation is the same.

The purpose of this module is to bring the CSSP out of Sleep mode into a previous known state. By storing values in the CSSP embedded RAM blocks, logic states (e.g., state machine states) can be retrieved upon wakeup and set to values that existed prior to entering Sleep mode.

Figure 1 shows a system level block diagram of the WAV PSB.

### **Functional and Module Description**

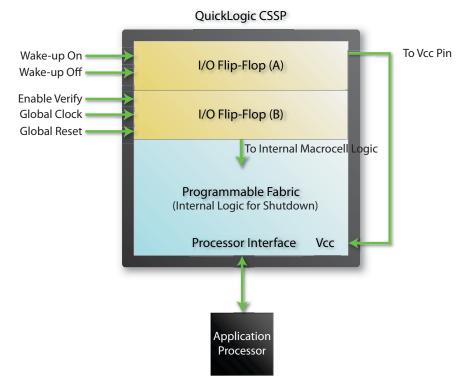

The WAV PSB consists of the following functional blocks as shown in Figure 2.

- I/O flip-flop (A) Controls the power to the core voltage. This requires dedicated external D-input, output, clock and reset pins.

- I/O flip-flop (B) Controls the external request to shut off the core voltage. This flip-flop uses the global reset and clock signals.

- **Processor interface** Communicates to the Host bus. It is responsible for decoding the local address of the transfer, and steering the transaction to the CSSP registers, internal SRAM, peripheral buses, or the USB Controller. Local bus byte lanes are assumed to be enabled at all times.

#### Figure 2: WAV PSB Block Diagram

# **Interface List and Description**

Table 1 summarizes the WAV PSB interface signals.

| Pin           | Type <sup>a</sup> | I/O Rail Voltage | Description                                                                      |

|---------------|-------------------|------------------|----------------------------------------------------------------------------------|

| General Signa |                   |                  |                                                                                  |

| Clock         | I                 | 1.8 V – 3.3 V    | Global system clock.                                                             |

| Reset         | I                 | 1.8 V – 3.3      | Global system reset.                                                             |

| Wake          | I                 | 1.8 V – 3.3 V    | Activates power to internal logic. Used in conjunction with Wake_En.             |

| Wake_En       | I                 | 1.8 V – 3.3 V    | Enables logic to enter low power Sleep mode. Used in conjunction with Wake mode. |

| Sleep_Rdy     | 0                 | 1.8 V – 3.3 V    | Optional. Denotes that the CSSP can be placed into Sleep mode.                   |

| Logic_Pwr     | 0                 | 1.8 V            | Power to Vcc pin (i.e., logic voltage).                                          |

| Sleep         | I                 | 1.8 V – 3.3 V    | Puts logic into low power Sleep mode.                                            |

| Vcc           | Pwr               | 1.8 V            | Logic voltage.                                                                   |

#### Table 1: Pin Descriptions

a. I = Input

O = Output

Pwr = Power

### **Power Consumption**

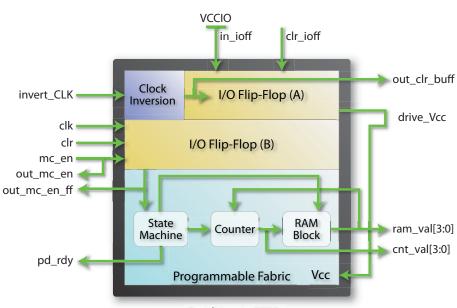

Figure 3 shows an example test design.

QuickLogic CSSP

| Table 2 summarizes the test de | esign pin descriptions. |

|--------------------------------|-------------------------|

|--------------------------------|-------------------------|

| Table 2: Test Design | Pin Descriptions |

|----------------------|------------------|

|----------------------|------------------|

| Pin          | Туре | Description                                                                                                                                                                                                                         |  |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCCIO        | I    | Input voltage tolerance pin.                                                                                                                                                                                                        |  |

| clk          | I    | The external global clock signal for the CSSP logic. It does not clock the dedicated I/O flip-flop that controls <i>drive_Vcc</i> .                                                                                                 |  |

| clr          | I    | The external global reset signal for the CSSP logic. It does not control the reset of the dedicated I/O flip-flop that controls <i>drive_Vcc</i> .                                                                                  |  |

| clk_ioff     |      | Clocked value of <i>in_ioff</i> on the falling-edge of <i>invert_CLK</i> .                                                                                                                                                          |  |

| clr_ioff     | I    | Clear signal for <i>drive_Vcc</i> and is connected to the CLR input of the dedicated I/O flip-flop. When high, voltage to the internal logic is shut off. When low, <i>invert_CLK</i> is enabled to turn on power to the CSSP core. |  |

| cnt_val[3:0] | 0    | Lower four bits of the test counter.                                                                                                                                                                                                |  |

| drive_Vcc    | Ο    | Drives the voltage to the core and is connected to the dedicated I/O flip-flo output.                                                                                                                                               |  |

| in_ioff      | I    | <i>drive_Vcc</i> is the clocked value of <i>in_ioff</i> on the falling-edge of <i>invert_clk</i> . The high to VCCIO.                                                                                                               |  |

| Pin          | Туре | Description                                                                                                                                                                                                             |  |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| invert_CLK   | I    | On its falling-edge, turns power on to the CSSP macrocell logic. The CSSP inverts this signal internally and sends it to the clock input of the I/O flip-flop controlling the CSSP macrocell power.                     |  |

| mc_en        | I    | The macrocell-enable signal and D-input to one of the dedicated I/O flip-flops.<br>When high, this notifies the CSSP that the internal logic is enabled. When low,<br>this signals to the CSSP to prepare for shutdown. |  |

| out_clr_buff | 0    | Buffered version of <i>clr_ioff</i> .                                                                                                                                                                                   |  |

| out_inv_clk  | 0    | Inverted version of <i>invert_CLK</i> .                                                                                                                                                                                 |  |

| out_mc_en    | 0    | Buffered version of <i>mc_en</i> .                                                                                                                                                                                      |  |

| out_mc_en_ff | 0    | Clocked (by <i>clk</i> ) version of <i>mc_en</i> .                                                                                                                                                                      |  |

| pd_rdy       | 0    | Indicates that the CSSP is ready for power-down of core.                                                                                                                                                                |  |

| ram_val[3:0] | 0    | Lower four bits of the RAM block.                                                                                                                                                                                       |  |

#### Table 2: Test Design Pin Descriptions (Continued)

The test design resulted in the following power measurements:

Conditions:

- clk 50 kHz, free-running

- VCCIO (all) 3.3 V

- VDD 1.8 V

- Vcc 1.8 V

#### Table 3: PolarPro II WLCSP-64 System Board

|                    | Vcc (Macrocell Voltage) = Hi (ON) |            |                    |            |            |

|--------------------|-----------------------------------|------------|--------------------|------------|------------|

| Dynamic Power      |                                   |            | Static Power       |            |            |

|                    | Vpump = Lo                        | Vpump = Hi |                    | Vpump = Lo | Vpump = Hi |

| I <sub>1.8V</sub>  | 93.1 µA                           | 14.8 µA    | I <sub>1.8V</sub>  | 85.4 μA    | 8.4 µA     |

| I <sub>V3.3V</sub> | 2.8 µA                            | 3.1 µA     | I <sub>V3.3V</sub> | 1.0 µA     | 1.2 µA     |

|                    | Vcc = Lo (OFF)                    |            |                    |            |            |

| Dynamic Power      |                                   |            | Static Power       |            |            |

|                    | Vpump = Lo                        | Vpump = Hi |                    | Vpump = Lo | Vpump = Hi |

| I <sub>1.8V</sub>  | 84.6 µA                           | 7.2 µA     | I <sub>1.8V</sub>  | 80.5 µA    | 2.6 µA     |

| I <sub>V3.3V</sub> | 1.2 µA                            | 1.3 µA     | I <sub>V3.3V</sub> | 1.0 µA     | 1.2 µA     |

The power savings when the macrocell logic voltage is off is minimal. This may have been due to the small size of the test design. If necessary, additional logic can be added to determine the power savings on larger designs.

**NOTE:** For maximum power savings, tie the CSSP Vpump pin to a 3.3 V source.

# **Supported Operating Systems**

The WAV PSB supports the following operating systems:

- Windows<sup>®</sup> CE

- Windows Mobile<sup>®</sup>

- $Linux^{\mathbb{R}}$

- $Android^{\mathbb{R}}$

# **Contact Information**

| Phone:    | (408) 990-4000 (US)          |

|-----------|------------------------------|

|           | (647) 367-1014 (Canada)      |

|           | +(44) 1932-21-3160 (Europe)  |

|           | +(886) 2-2345-5600 (Taiwan)  |

|           | +(86) 21-5116-0532 (China)   |

| E-mail:   | info@quicklogic.com          |

| Sales:    | America-sales@quicklogic.com |

|           | Europe-sales@quicklogic.com  |

|           | Asia-sales@quicklogic.com    |

|           | Japan-sales@quicklogic.com   |

| Support:  | www.quicklogic.com/support   |

| Internet: | www.quicklogic.com           |

# **Revision History**

| Revision | Date      | Originator and Comments                       |

|----------|-----------|-----------------------------------------------|

| A        | July 2010 | Andy Green, Paul Karazuba and Kathleen Bylsma |

### **Notice of Disclaimer**

QuickLogic is providing this design, product or intellectual property "as is." By providing the design, product or intellectual property as one possible implementation of your desired system-level feature, application, or standard, QuickLogic makes no representation that this implementation is free from any claims of infringement and any implied warranties of merchantability or fitness for a particular purpose. You are responsible for obtaining any rights you may require for your system implementation. QuickLogic shall not be liable for any damages arising out of or in connection with the use of the design, product or intellectual property including liability for lost profit, business interruption, or any other damages whatsoever. QuickLogic products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use QuickLogic products in these types of equipment or applications.

QuickLogic does not assume any liability for errors which may appear in this document. However, QuickLogic attempts to notify customers of such errors. QuickLogic retains the right to make changes to either the documentation, specification, or product without notice. Verify with QuickLogic that you have the latest specifications before finalizing a product design.

## **Copyright and Trademark Information**

Copyright © 2010 QuickLogic Corporation. All Rights Reserved.

The information contained in this document is protected by copyright. All rights are reserved by QuickLogic Corporation. QuickLogic Corporation reserves the right to modify this document without any obligation to notify any person or entity of such revision. Copying, duplicating, selling, or otherwise distributing any part of this product without the prior written consent of an authorized representative of QuickLogic is prohibited.

QuickLogic and ViaLink are registered trademarks; and the QuickLogic logo is a trademark of QuickLogic. Other trademarks are the property of their respective companies.