**QUICKLOGIC CORPORATION**

# S3 Technical Reference Manual (TRM)

S3 Architecture

Revision 1.01a

# **Notice of Disclaimer**

QuickLogic is providing this design, product or intellectual property "as is." By providing the design, product or intellectual property as one possible implementation of your desired system-level feature, application, or standard, QuickLogic makes no representation that this implementation is free from any claims of infringement and any implied warranties of merchantability or fitness for a particular purpose. You are responsible for obtaining any rights you may require for your system implementation. QuickLogic shall not be liable for any damages arising out of or in connection with the use of the design, product or intellectual property including liability for lost profit, business interruption, or any other damages whatsoever. QuickLogic products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use QuickLogic products in these types of equipment or applications.

QuickLogic does not assume any liability for errors which may appear in this document. However, QuickLogic attempts to notify customers of such errors. QuickLogic retains the right to make changes to either the documentation, specification, or product without notice. Verify with QuickLogic that you have the latest specifications before finalizing a product design.

# **Copyright and Trademark Information**

Copyright © 2020 QuickLogic Corporation. All Rights Reserved.

The information contained in this document is protected by copyright. All rights are reserved by QuickLogic Corporation. QuickLogic Corporation reserves the right to modify this document without any obligation to notify any person or entity of such revision. Copying, duplicating, selling, or otherwise distributing any part of this product without the prior written consent of an authorized representative of QuickLogic is prohibited.

QuickLogic is a registered trademark. EOS, the EOS design and the QuickLogic logo is a trademark of QuickLogic. Other trademarks are the property of their respective companies.

TrulyHandsfree<sup>™</sup> is a registered trademark of Sensory, Inc.

This document is intended to be used by system hardware engineers and low-level software/firmware developers.

# Contents

| Introductio    | on                                                               | 17 |

|----------------|------------------------------------------------------------------|----|

| СНАРТЕ         | R 1. EOS S3 SENSOR PROCESSING PLATFORM KEY FEATURES              | 17 |

| 1.1            | Features List                                                    | 17 |

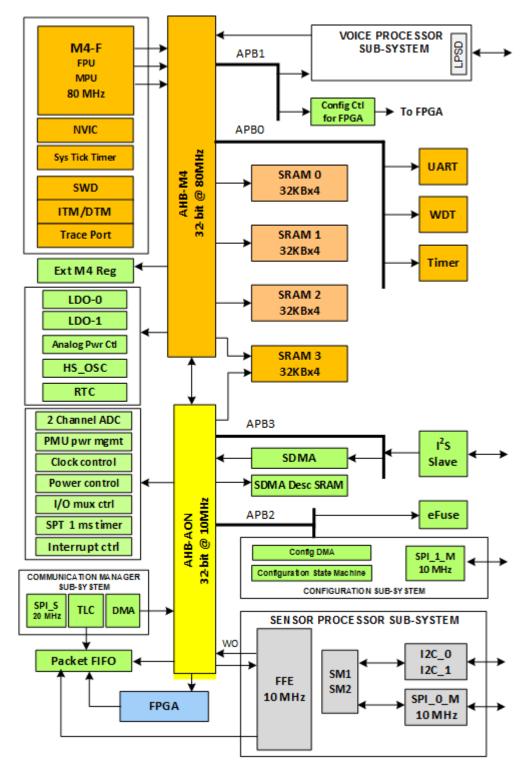

| СНАРТЕ         | R 2. THE S3 HIGH-LEVEL ARCHITECTURE                              | 22 |

| 2.1            | S3 block diagram with main sub-systems                           |    |

| 2.2            | The top-level internal system elements and peripherals in the S3 |    |

| 2.2.1          |                                                                  |    |

| 2.2.2          | 2 List by functional groups                                      | 25 |

| 2.2.3          | 5 1 1                                                            |    |

| 2.3            | Key blocks in the main sub-systems                               |    |

| 2.3.1<br>2.3.2 |                                                                  |    |

| 2.3.2          |                                                                  |    |

| 2.3.4          | •                                                                |    |

| 2.3.5          |                                                                  |    |

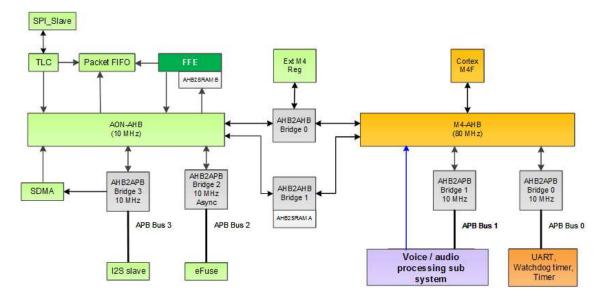

| 2.4            | Buses in the S3: AHB, secondary buses, and bridges               |    |

| 2.5            | Memory concepts in the S3 architecture                           |    |

| 2.5.1          |                                                                  |    |

| 2.5.2<br>2.5.3 |                                                                  |    |

| 2.5.4          |                                                                  |    |

| 2.6            | Support for designs with an Applications Processor               |    |

|                | Support for standalone designs (Host Mode operation)             |    |

|                |                                                                  |    |

| ARM Corte      | ex-M4F Sub-System & Core IO                                      | 31 |

|                |                                                                  |    |

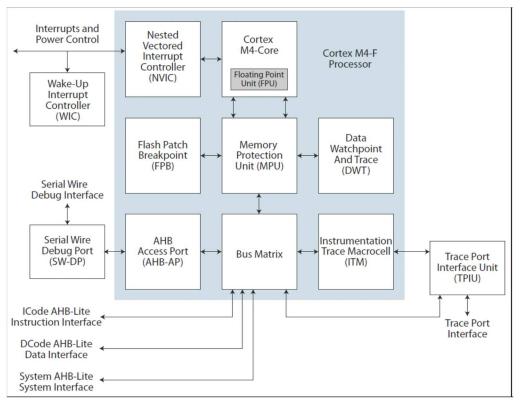

| CHAPTER        | R 3. ARM CORTEX-M4F SUB-SYSTEM                                   | 31 |

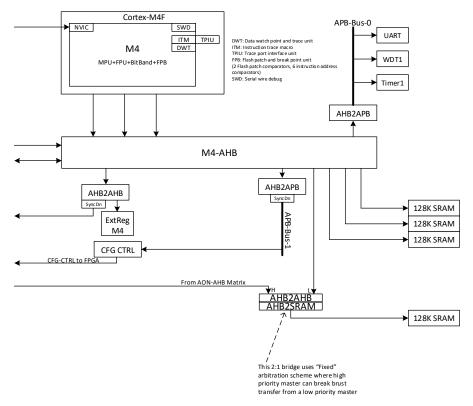

| 3.1            | Description                                                      | 31 |

| 3.2            | ARM Cortex-M4-F IP Configuration                                 | 32 |

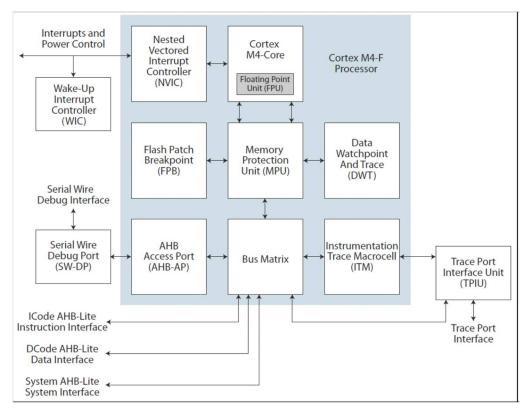

| 3.3            | ARM Cortex-M4-F Processor                                        | 33 |

| 3.3.1          | Cortex-M4-F Processor Block Diagram                              | 33 |

| 3.3.2          |                                                                  |    |

| 3.4            | Cortex-M4-F Core Peripherals                                     | 34 |

| 3.4.1          |                                                                  |    |

| 3.4.2          |                                                                  |    |

| 3.5            | Buses                                                            | -  |

| 3.5.1<br>3.5.2 |                                                                  |    |

| 3.6            | Memory                                                           |    |

| 3.6.1          | •                                                                |    |

| 3.6.2          |                                                                  |    |

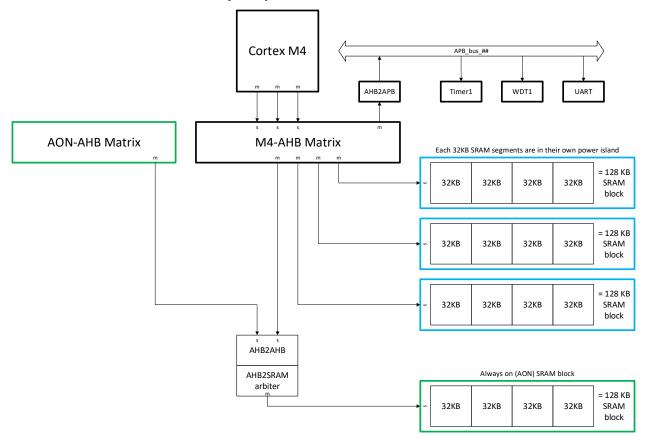

| 3.6.3 M4 SRAM                                                    | 44  |

|------------------------------------------------------------------|-----|

| 3.6.3.1 SRAM Configuration                                       |     |

| 3.6.3.2 Registers                                                |     |

| 3.7 Memory Protection Unit (MPU)                                 |     |

| 3.7.1 MPU Registers                                              |     |

| 3.8 Nested Vectored Interrupt Controller (NVIC)                  |     |

| 3.8.1 List of interrupts                                         |     |

| 3.8.2 NVIC Registers                                             |     |

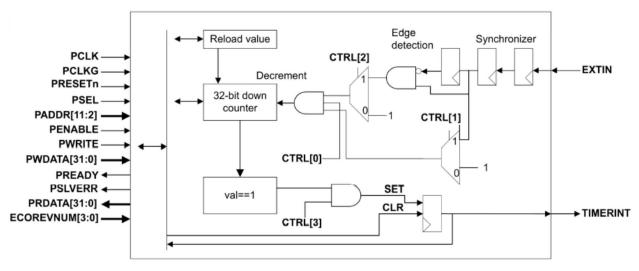

| 3.9 Timers                                                       |     |

| 3.9.1 M4 Timer                                                   | -   |

| 3.9.3 SysTick Timer                                              |     |

| 3.9.4 SysTick Register                                           |     |

| 3.9.5 Watchdog Timer (WDT)                                       |     |

| 3.9.6 WDT Registers                                              | 56  |

| CHAPTER 4. SYSTEM BUSES                                          | 58  |

| 4.1 M4 AHB bus                                                   | .58 |

| 4.2 AON AHB bus                                                  | .58 |

| 4.3 AHB2APB bus bridges                                          |     |

| CHAPTER 5. MEMORY                                                |     |

| 5.1 SRAM                                                         | .59 |

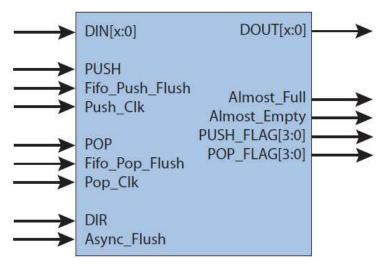

| 5.2 FIFOs                                                        |     |

| 5.3 Packet FIFO                                                  |     |

| 5.3.1 Registers                                                  |     |

| -                                                                |     |

| CHAPTER 6. DMA                                                   |     |

| 6.1 System DMA Controller (SDMA)                                 |     |

| 6.1.1 SDMA Registers<br>6.1.2 SDMA BRIDGE Registers              |     |

| 6.2 VP DMAC                                                      |     |

| 6.2.1 VP DMAC registers                                          |     |

|                                                                  |     |

| CHAPTER 7. INTERRUPT HARDWARE                                    |     |

| 7.1 Wake-up Interrupt Controller (WIC)                           | .79 |

| 7.1.1 Registers                                                  | 79  |

| CHAPTER 8. ON-CHIP LDO POWER REGULATION                          | 80  |

| 8.1 LDO                                                          | .80 |

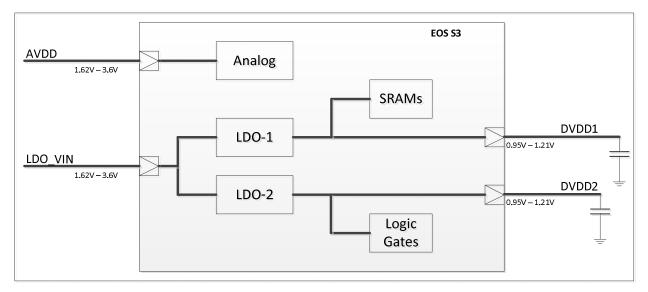

| 8.1.1 Design case: Internal Voltages Supplied by Two LDOs        | 80  |

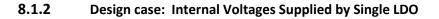

| 8.1.2 Design case: Internal Voltages Supplied by Single LDO      |     |

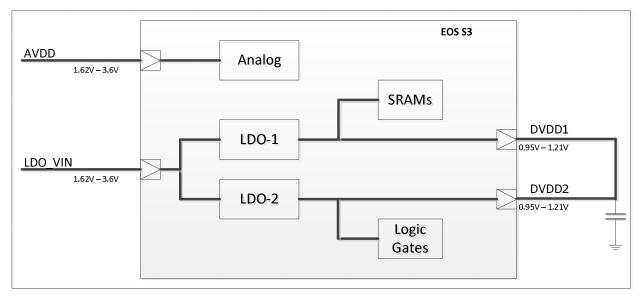

| 8.1.3 Design case: Internal Voltages Supplied by External Source | 82  |

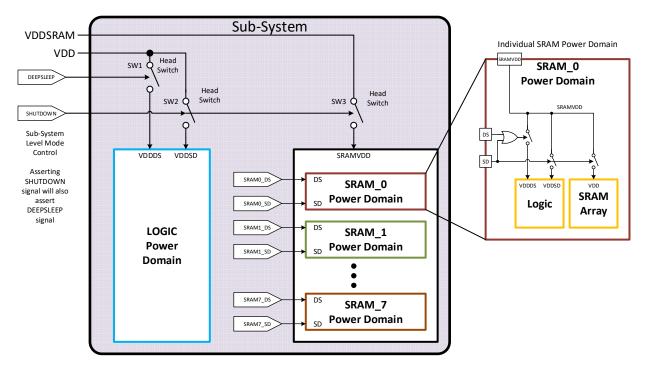

| CHAPTER 9. POWER DOMAINS IN THE S3                               | 83  |

| 9.1 Main power domains in the S3                                 | .83 |

| 9.1.1 AON A0 Always ON power domain                              |     |

| 9.1.2 A1 domain                                                  | 84  |

| 9.1                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9.1                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                     |

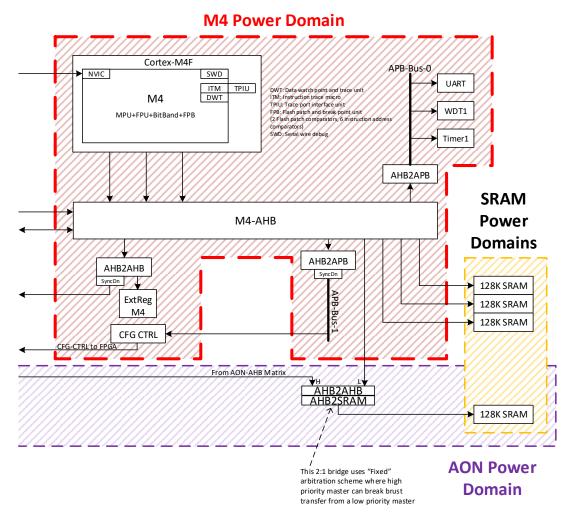

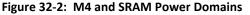

| 9.2                                                                                                                 | SRAM Power Domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85                                                                                                                                                                                                                                                                                                                                                  |

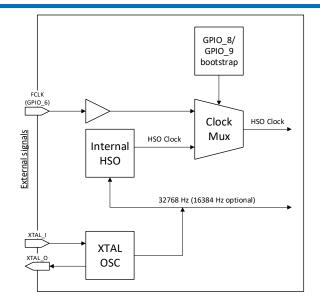

| CHAPT                                                                                                               | TER 10. CLOCK OSCILLATORS, SYSTEM CLOCKS, AND TIMERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 86                                                                                                                                                                                                                                                                                                                                                  |

| 10.1                                                                                                                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 86                                                                                                                                                                                                                                                                                                                                                  |

| 10.2                                                                                                                | Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 86                                                                                                                                                                                                                                                                                                                                                  |

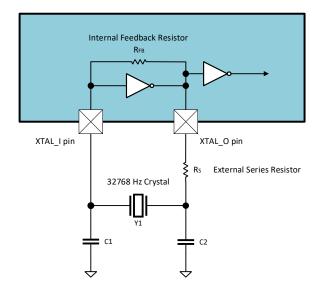

| 10.                                                                                                                 | 0.2.1 The Slow Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                     |

| :                                                                                                                   | 10.2.1.1 Design using crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                     | 10.2.1.2 Design using external clock instead of crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86                                                                                                                                                                                                                                                                                                                                                  |

| 10.                                                                                                                 | 0.2.2 The Fast Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                     |

| :                                                                                                                   | 10.2.2.1 Frequency selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                     |

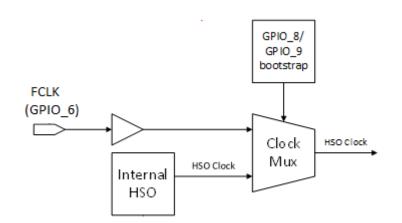

| :                                                                                                                   | 10.2.2.2 Selection of source for internal HSO_Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                                                                                                                                                                                                                                                                                                                                  |

| CHAPT                                                                                                               | TER 11. CLOCK DOMAINS, CLOCK CHAINS, AND THE CRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                                                                                                                                                                                                                                                                                                                                  |

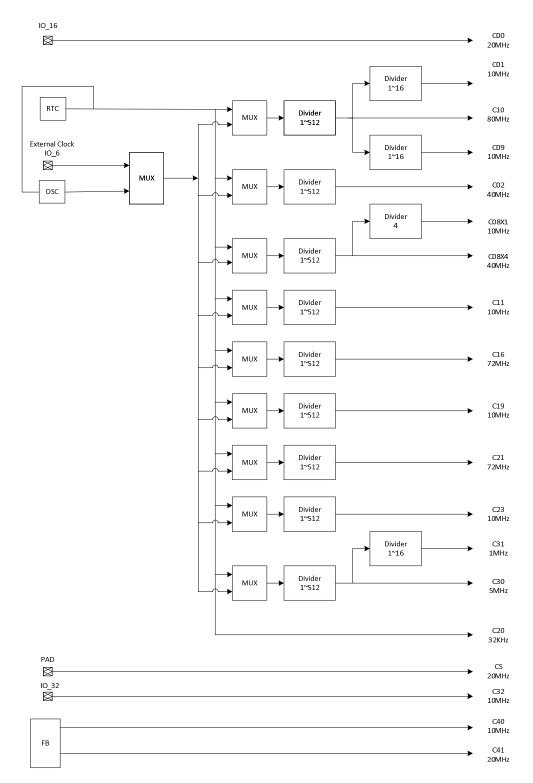

| 11.1                                                                                                                | Clock sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88                                                                                                                                                                                                                                                                                                                                                  |

| 11.2                                                                                                                | Clock divider chains and the CRU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                                                                                                                                                                                                                                                                                                                                  |

| 11.                                                                                                                 | 1.2.1 Clock Gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93                                                                                                                                                                                                                                                                                                                                                  |

| 11.3                                                                                                                | Clock Reset Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 93                                                                                                                                                                                                                                                                                                                                                  |

| 11.                                                                                                                 | 1.3.1 CRU Control Register Background Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                     |

| 11.                                                                                                                 | 1.3.2 CRU Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                     |

| Core Spe                                                                                                            | ecial IO Functions & GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 112                                                                                                                                                                                                                                                                                                                                                 |

| Core Spe                                                                                                            | ecial IO Functions & GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 112                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                     | ecial IO Functions & GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                     |

| CHAPT                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 112                                                                                                                                                                                                                                                                                                                                                 |

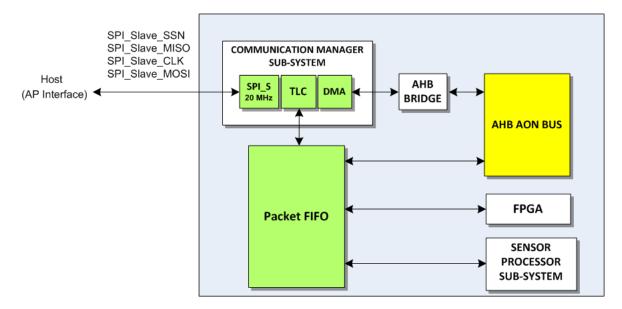

| CHAPT                                                                                                               | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 112<br>113                                                                                                                                                                                                                                                                                                                                          |

| CHAPT<br>CHAPT<br>13.1                                                                                              | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW<br>TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM<br>CM Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 112<br>113<br>                                                                                                                                                                                                                                                                                                                                      |

| CHAPT<br>CHAPT<br>13.1<br>13.                                                                                       | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 112<br>113<br>                                                                                                                                                                                                                                                                                                                                      |

| CHAPT<br>CHAPT<br>13.1<br>13.                                                                                       | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                     |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2                                                                        | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>112</b><br><b>113</b><br><b>113</b><br><b>113</b><br>113<br>114<br><b>114</b>                                                                                                                                                                                                                                                                    |

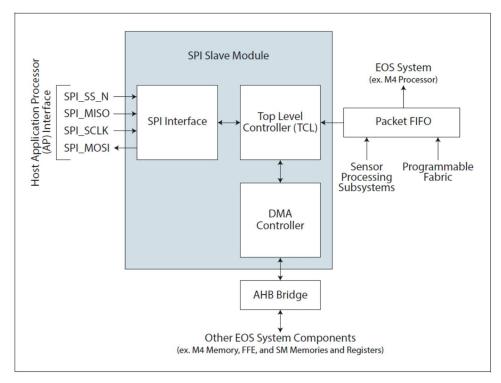

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT                                                               | <ul> <li>TER 12. CORE SPECIAL IO FUNCTIONS &amp; GPIO OVERVIEW</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>115                                                                                                                                                                                                                                                                                         |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1                                                       | <ul> <li>TER 12. CORE SPECIAL IO FUNCTIONS &amp; GPIO OVERVIEW</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>115<br>115                                                                                                                                                                                                                                                                                  |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2                                                      | <ul> <li>TER 12. CORE SPECIAL IO FUNCTIONS &amp; GPIO OVERVIEW</li> <li>TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM</li> <li>CM Architecture</li> <li>3.1.1 Top Level Controller in the CM</li> <li>3.1.2 Communication Manager DMA controller</li> <li>Communication Manager Theory of Operation</li> <li>TER 14. SPI_SLAVE INTERFACE IN THE CM</li> <li>Introduction</li> <li>Architecture</li> </ul>                                                                                                                                                                                                                                                                                                                                            | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>115<br>115                                                                                                                                                                                                                                                                                  |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3                                              | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles                                                                                                                                                                                                                                                                                                                                                        | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>115<br>115<br>115<br>115                                                                                                                                                                                                                                                             |

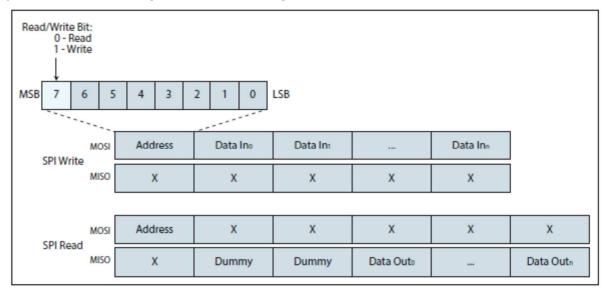

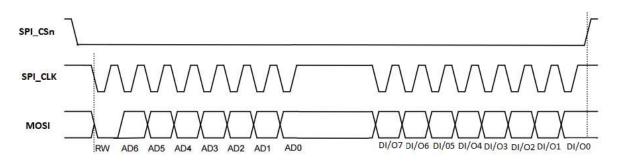

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4                               | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture.         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller.         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture.         Usage Roles         SPI Interface Protocol for the SPI_Slave block                                                                                                                                                                                                                                                                                              | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>115<br>115<br>115<br>115<br>115<br>115                                                                                                                                                                                                                                               |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5                              | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture.         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller.         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture.         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers                                                                                                                                                                                                                                                           | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>115<br>115<br>115<br>115<br>115<br>115                                                                                                                                                                                                                                               |

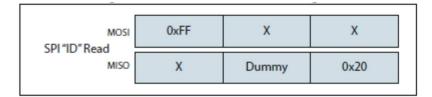

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.                       | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1                                                                                                                                                                                                                                                | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>115<br>115<br>115<br>115<br>115<br>115                                                                                                                                                                                                                                               |

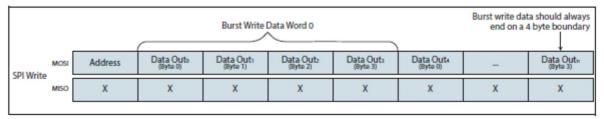

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.<br>14.         | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture.         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller.         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture.         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1 Device ID Read         4.5.2 Transfer Types                                                                                                                                                                                                 | 112<br>113<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>115<br>115<br>115<br>115<br>115<br>115                                                                                                                                                                                                                                               |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.<br>14.<br>14.5 | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1 Device ID Read         4.5.2 Transfer Types         14.5.2.1 Transfers to TLC Local Registers                                                                                                                                                  | 112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>115<br>115<br>115<br>115<br>115<br>116<br>116<br>117<br>118                                                                                                                                                                                                                                 |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.<br>14.         | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1 Device ID Read         4.5.2 Transfer Types         14.5.2.1 Transfers to TLC Local Registers         14.5.2.2 Transfer Strom Packet FIFOs                                                                                                     | 112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>115<br>115<br>115<br>115<br>115<br>115                                                                                                                                                                                                                                                      |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.<br>14.                | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1 Device ID Read         4.5.2 Transfer Types         14.5.2.1 Transfers to TLC Local Registers         14.5.2.2 Transfers from Packet FIFOs         14.5.2.3 Transfers to M4 Memory Address Space                                               | 112         113         113         113         113         113         113         113         113         113         114         114         114         114         114         114         115         115         115         115         115         115         116         117         118         118         118         118             |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.<br>14.<br>14.  | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1 Device ID Read         4.5.2 Transfer Types         14.5.2.1 Transfers to TLC Local Registers         14.5.2.2 Transfers from Packet FIFOs         14.5.2.3 Transfers to M4 Memory Address Space         4.5.3 Basic AHB Transfer Restrictions | 112         113         113         113         113         113         113         113         114         114         114         114         115         115         115         115         116         117         118         118         118         118         118         118                                                             |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.<br>14.<br>14.  | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1 Device ID Read         4.5.2 Transfer Types         14.5.2.3 Transfers to TLC Local Registers         14.5.2.3 Transfer Restrictions         14.5.3.1 AHB Memory Read                                                                          | 112         113         113         113         113         113         113         113         114         114         114         114         115         115         115         115         115         116         117         118         118         118         118         118         118         119                                     |

| CHAPT<br>CHAPT<br>13.1<br>13.<br>13.<br>13.2<br>CHAPT<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.<br>14.<br>14.  | TER 12. CORE SPECIAL IO FUNCTIONS & GPIO OVERVIEW         TER 13. COMMUNICATION MANAGER (CM) SUB-SYSTEM         CM Architecture         3.1.1 Top Level Controller in the CM         3.1.2 Communication Manager DMA controller         Communication Manager Theory of Operation         TER 14. SPI_SLAVE INTERFACE IN THE CM         Introduction         Architecture         Usage Roles         SPI Interface Protocol for the SPI_Slave block         Basic Read/Write Transfers         4.5.1 Device ID Read         4.5.2 Transfer Types         14.5.2.1 Transfers to TLC Local Registers         14.5.2.2 Transfers from Packet FIFOs         14.5.2.3 Transfers to M4 Memory Address Space         4.5.3 Basic AHB Transfer Restrictions | 112         113         113         113         113         113         113         113         113         114         114         114         114         114         114         114         115         115         115         115         115         115         116         117         118         118         118         118         119 |

| 14.6 Communication Manager Components Registers                 | 121 |

|-----------------------------------------------------------------|-----|

| CHAPTER 15. UART                                                |     |

| 15.1 UART registers                                             | 124 |

| CHAPTER 16. CLOCKING AND TIMING ELEMENTS                        | 133 |

| 16.1 RTC (Real Time Clock)                                      |     |

| 16.1.1 RTC Registers                                            |     |

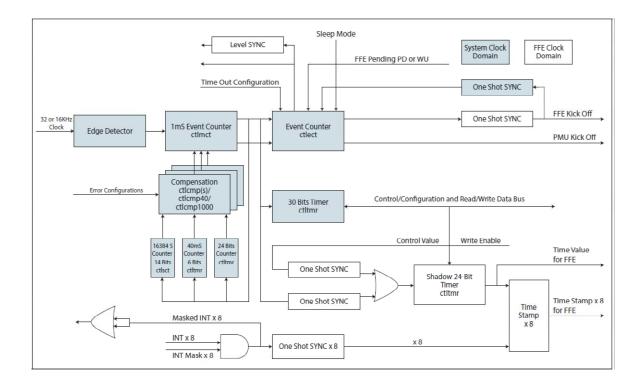

| 16.2 SPT (Simple Periodic Timer)                                | 133 |

| 16.2.1 Error Correction for 1mS Timer                           | 134 |

| 16.2.2 Timeout Event Counter                                    |     |

| 16.2.3 Time Stamp Counters                                      |     |

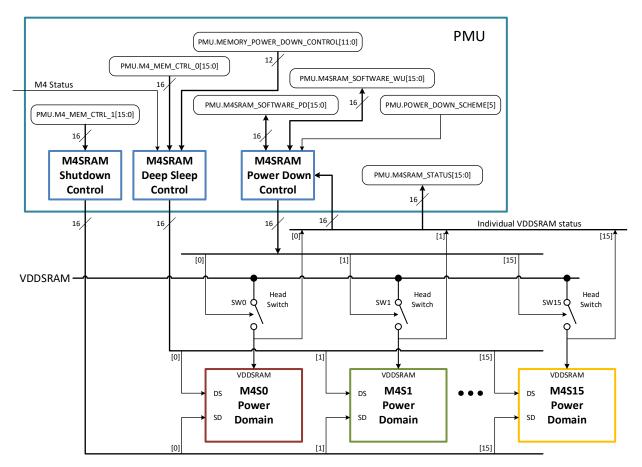

| 16.2.4 PMU and FFE Wakeup                                       |     |

| 16.2.5 Registers for SPT and RTC                                |     |

| CHAPTER 17. ANALOG IP (AIP) BLOCK                               |     |

| 17.1 Real time clock                                            |     |

| 17.2 HS_OSC                                                     | 144 |

| 17.3 APC                                                        | 144 |

| 17.4 LDO                                                        | 144 |

| 17.5 AIP group registers                                        | 144 |

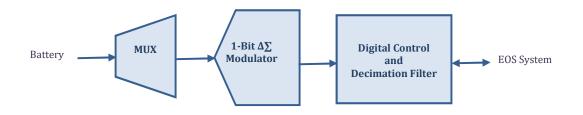

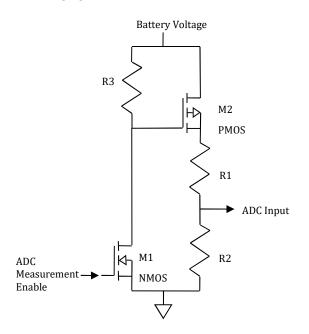

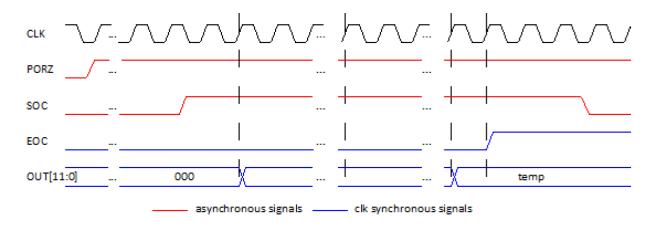

| CHAPTER 18. ANALOG-TO-DIGITAL CONVERTER (ADC)                   | 151 |

| 18.1.1 Overview                                                 |     |

| 18.1.2 Functional Description                                   | 151 |

| 18.1.3 PCB Layout Recommendations                               | 151 |

| 18.1.4 Example Application                                      |     |

| 18.1.5 ADC Registers                                            | 152 |

| CHAPTER 19. S3 GPIO                                             | 153 |

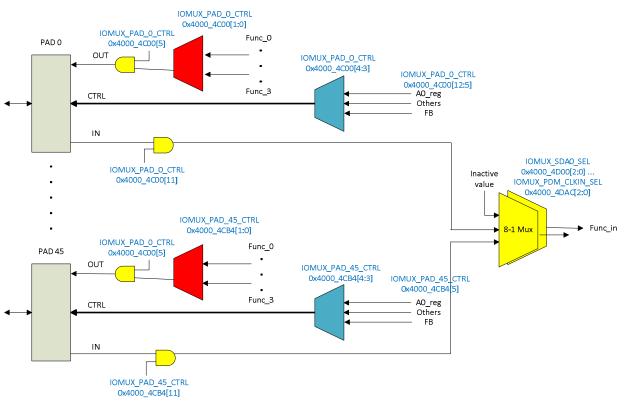

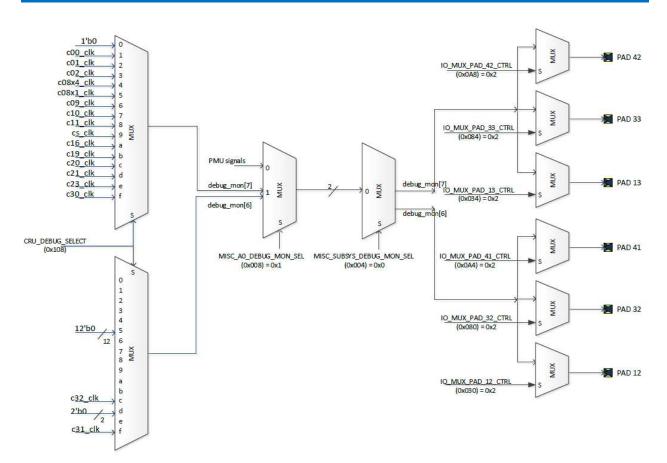

| 19.1 IO Mux and GPIO Introduction                               | 153 |

| 19.2 IO Mux Overview                                            | 153 |

| 19.3 How to Select Output Function                              | 154 |

| 19.4 Selecting an Input Function                                | 158 |

| 19.5 IOMux Assignments                                          | 161 |

| 19.6 GPIO Registers                                             | 170 |

| 19.6.1 PAD_x CTRL register Description                          | 211 |

|                                                                 |     |

| Voice / Audio Processing subsystem                              |     |

| CHAPTER 20. VOICE / AUDIO PROCESSING SUB-SYSTEM                 | 212 |

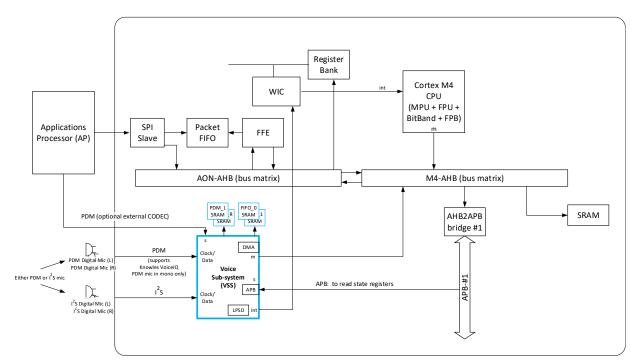

| 20.1 Introduction                                               | 212 |

| 20.1.1 General characteristics                                  | 212 |

| 20.1.2 Power                                                    |     |

| 20.1.3 List of operating modes                                  |     |

| 20.1.4 Application example in system with Application Processor | 213 |

QuickLogic

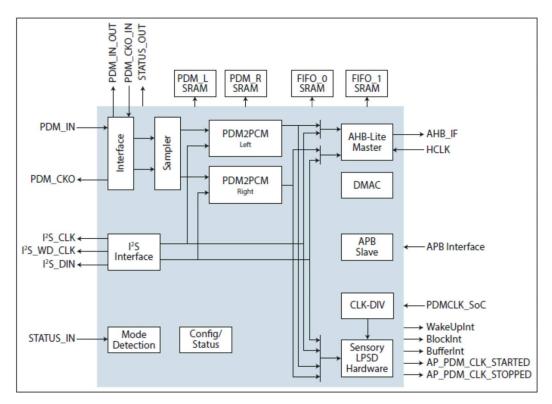

| 20.2 Sub-system Architecture                                                                                            | 214 |

|-------------------------------------------------------------------------------------------------------------------------|-----|

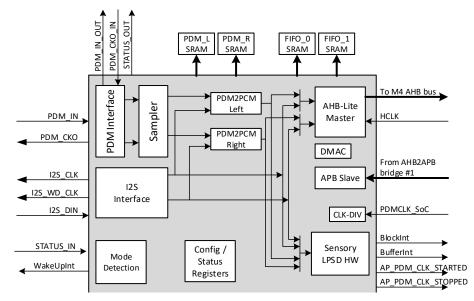

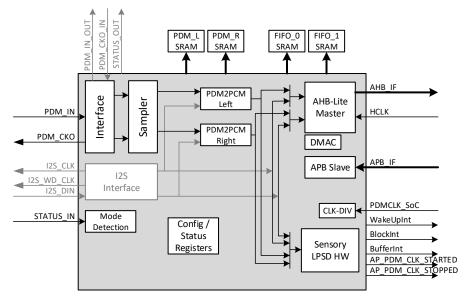

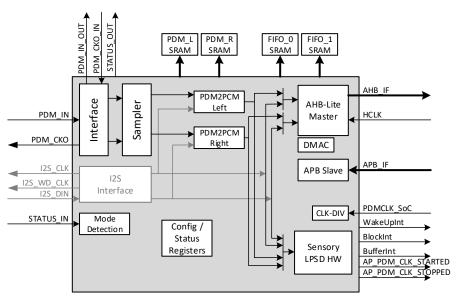

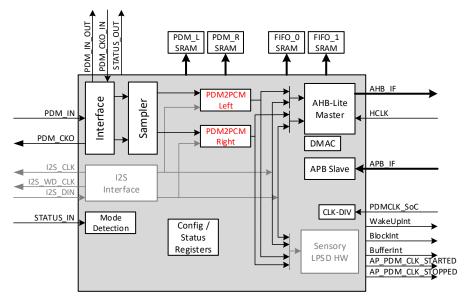

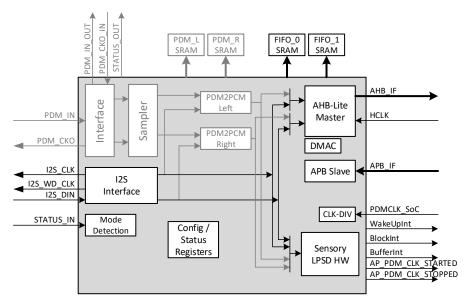

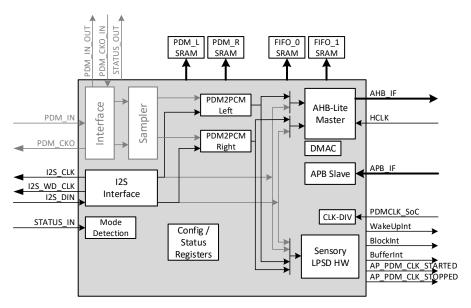

| 20.2.1 Voice / Audio Processing sub-system internal block diagram                                                       | 214 |

| 20.2.1.1 Pulse Density Modulation (PDM) Interface                                                                       | 215 |

| 20.2.1.2 Inter-IC Sound (I <sup>2</sup> S) Interface                                                                    |     |

| 20.2.1.3 Low-Power Sound Detect (LPSD)                                                                                  |     |

| 20.2.2 PDM Internal CODEC Mode                                                                                          |     |

| 20.2.3 PDM External CODEC Mode<br>20.2.4 PDM VoiceQ Mode                                                                |     |

| 20.2.4 PDM VoiceQ Mode                                                                                                  |     |

| 20.2.6 I <sup>2</sup> S Sub-Sample Mode                                                                                 |     |

| 20.3 Voice / audio processing sub-system registers                                                                      |     |

|                                                                                                                         |     |

| Sensor Processing Hub Sub-system                                                                                        | 225 |

| CHAPTER 21. SENSOR PROCESSING HUB SUB-SYSTEM                                                                            | 225 |

| 21.1 Introduction                                                                                                       |     |

|                                                                                                                         |     |

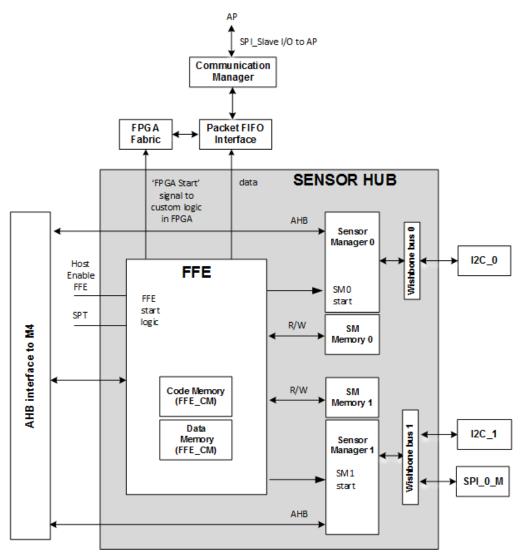

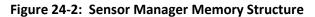

| 21.2 Sensor Processing Hub Sub-System Architecture                                                                      |     |

| 21.2.1 Block diagram                                                                                                    |     |

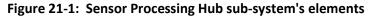

| 21.2.2 Key elements in the Sensor Processing Hub sub-system<br>21.2.2.1 AHB master bridge for the Sensor Processing Hub |     |

| 21.2.3 Related system components: Packet FIFO                                                                           |     |

| 21.3 General characteristics                                                                                            |     |

|                                                                                                                         |     |

| <ul><li>21.3.1 Key functional characteristics</li><li>21.3.2 Power</li></ul>                                            |     |

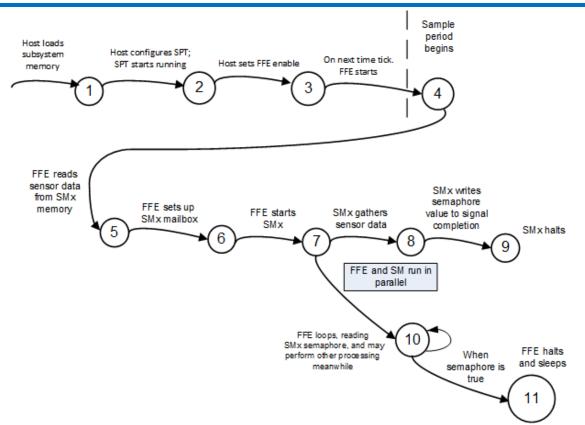

| CHAPTER 22. SENSOR PROCESSING HUB THEORY OF OPERATION                                                                   | 229 |

| 22.1 Control and Flow                                                                                                   |     |

| 22.1.1 Operating flow                                                                                                   |     |

| 22.1.2 SM Mailboxes                                                                                                     |     |

| 22.2 Sampling and Timing                                                                                                | 231 |

| 22.2.1 Time Stamping                                                                                                    | 231 |

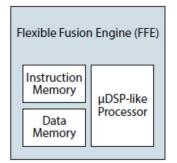

| CHAPTER 23. FLEXIBLE FUSION ENGINE (FFE)                                                                                | 232 |

| 23.1 Architecture of the FFE                                                                                            | 232 |

| 23.1.1 μDSP general functions                                                                                           |     |

| 23.1.2 Instruction Memory                                                                                               |     |

| 23.1.3 Data Memory                                                                                                      | 233 |

| 23.2 Theory of operation for the FFE                                                                                    | 233 |

| 23.2.1 Power control                                                                                                    |     |

| 23.2.2 Mailboxes                                                                                                        | -   |

| 23.2.3 Data handling                                                                                                    | 234 |

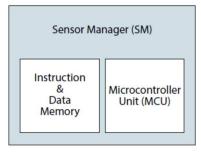

| CHAPTER 24. SENSOR MANAGERS                                                                                             | 235 |

| 24.1 Sensor Manager Internal Architecture                                                                               |     |

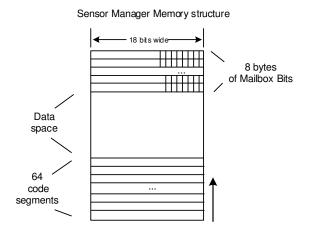

| 24.1.1 Sensor Manager Memory                                                                                            |     |

| 24.1.1.1 Structure of Sensor Manager memory                                                                             | 235 |

| 24.2 Related system elements                                                                                            | 236 |

| 24.2.1 Wishbone Bus                                                             |     |

|---------------------------------------------------------------------------------|-----|

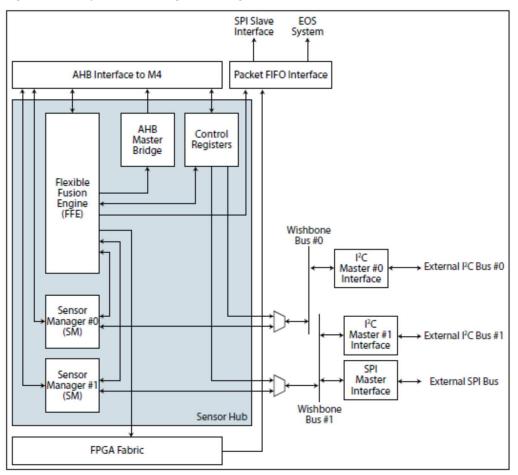

| $24.2.2  I^2 C \text{ interfaces } \dots$                                       |     |

| 24.2.2.1 I <sup>2</sup> C Master 0                                              |     |

| 24.2.2.2 I <sup>2</sup> C Master 1                                              |     |

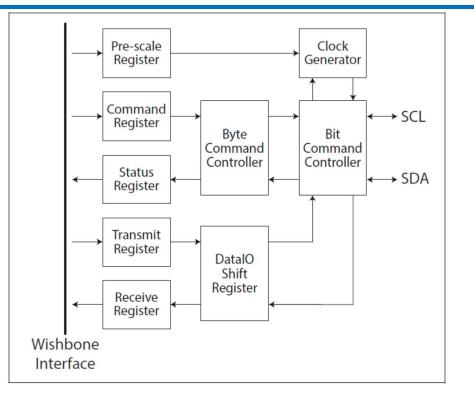

| 24.2.3 SPI_0_Master                                                             |     |

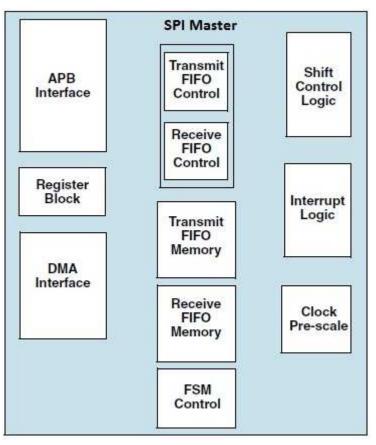

| CHAPTER 25. SPI_0_MASTER                                                        |     |

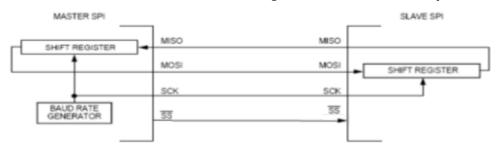

| 25.1 Architecture and Operation                                                 |     |

| 25.2 I/O signals for the SPI_0_Master block                                     | 239 |

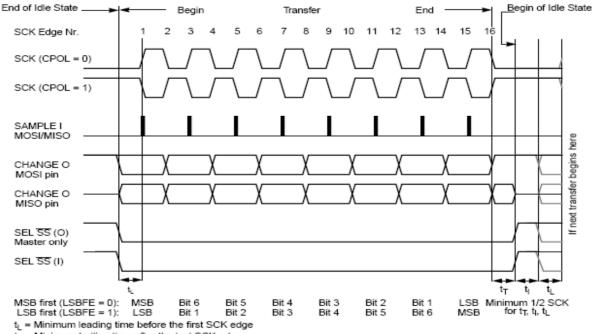

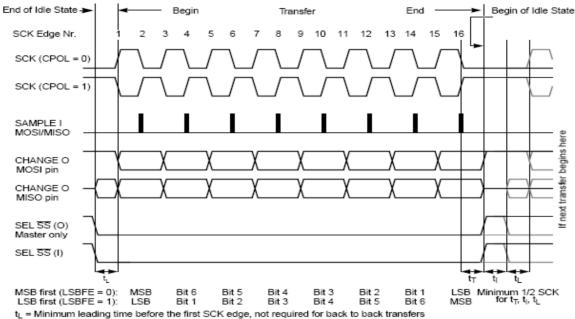

| 25.3 Master / slave clocking                                                    | 240 |

| 25.4 SPI Transactions                                                           | 240 |

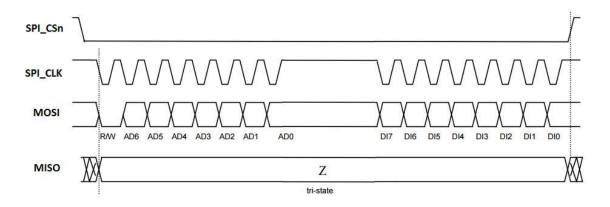

| 25.4.1 SPI Write Cycle                                                          |     |

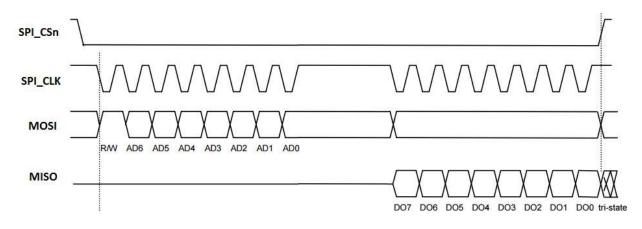

| 25.4.2 SPI Read Cycle                                                           |     |

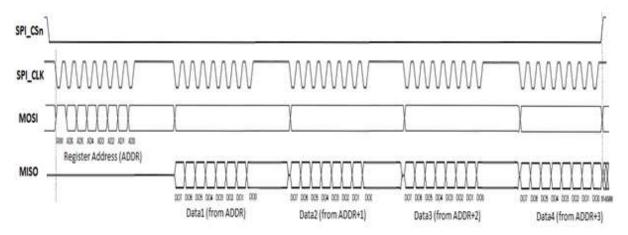

| 25.4.3 SPI Multiple Read Cycle                                                  |     |

| 25.4.5 SPI 3 wire configuration                                                 |     |

| 25.4.6 SPI corner cases                                                         |     |

| 25.4.7.1 Transfer Format for CPHA = 0                                           |     |

| 25.4.7.2 Transfer Format for CPHA = 1                                           |     |

| 25.5 SPI 0 Master Registers                                                     |     |

| 25.5.1 Address Map                                                              |     |

| 25.5.2 Register Descriptions                                                    |     |

| 25.5.2.1 Register: SPI Baud Register LSB (SPIBR LSB) (Offset 0x00)              |     |

| 25.5.2.2 Register: SPI Baud Register MSB (SPIBR MSB) (Offset 0x01)              |     |

| 25.5.2.3 SPI Configuration Register (offset 0x02)                               |     |

| 25.5.2.4 SPI Configuration Register (SPICR) (Offset 0x02)                       |     |

| 25.5.2.5 Transmit Register (Offset 0x03) - Write only                           |     |

| 25.5.2.6 Receive Register (Offset 0x03) -Read Only                              |     |

| 25.5.2.7 SPI Command (Transfer) Register (Offset 0x04) -Write Only              |     |

| 25.5.2.8 SPI Interrupt / Status Register (Offset 0x04) -Read Only               |     |

| 25.5.2.9 Slave Select Register (Offset 0x05)                                    |     |

| 25.5.2.10 SPI bit / clock control register (Offset 0x06)                        | 250 |

| 25.5.2.11 Number of SPI clocks required after CSn is de-activated (Offset 0x07) |     |

| 25.6 Programming                                                                | 251 |

| 25.6.1 SPI Host Operation                                                       | 251 |

| 25.6.2 Read Operation                                                           | 251 |

| 25.6.3 Write Operation                                                          | 252 |

| CHAPTER 26. SENSOR SUB-SYSTEM REGISTERS                                         | 253 |

| 26.1 FFE registers                                                              | 253 |

| FPGA Sub-system                                                                 |     |

|                                                                                 |     |

| CHAPTER 27. FPGA SUB-SYSTEM                                                     | 261 |

| 27.1 Introduction                                                               |     |

| 27.1.1 Power                                                                    |     |

| 27.2 Sub-system Architecture                                                    |     |

QuickLogic

| 27.2.1 FPGA sub-system components                                                    | 261 |

|--------------------------------------------------------------------------------------|-----|

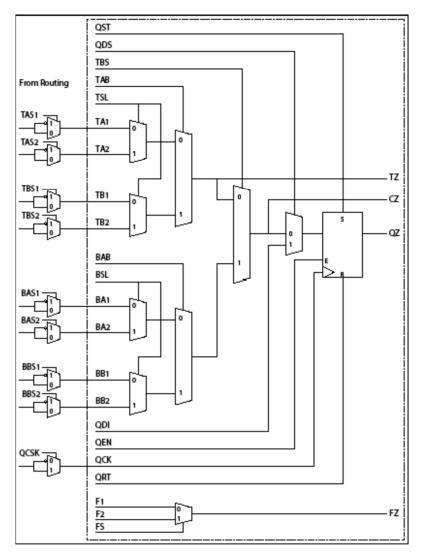

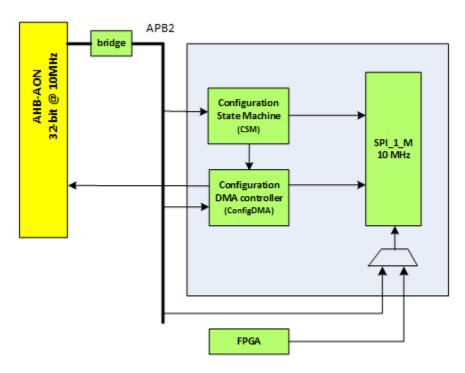

| 27.2.2 Functional Description                                                        | 262 |

| 27.2.2.1 Logic Cell                                                                  | 262 |

| 27.2.2.2 RAM/FIFO                                                                    |     |

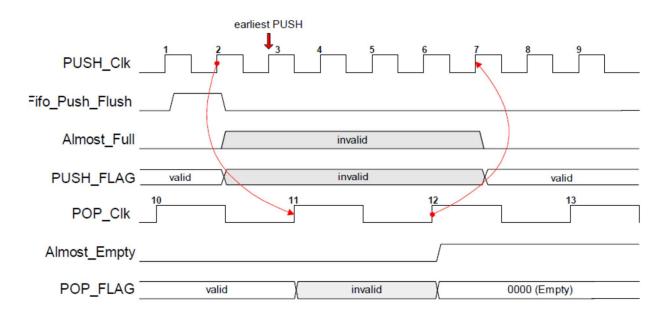

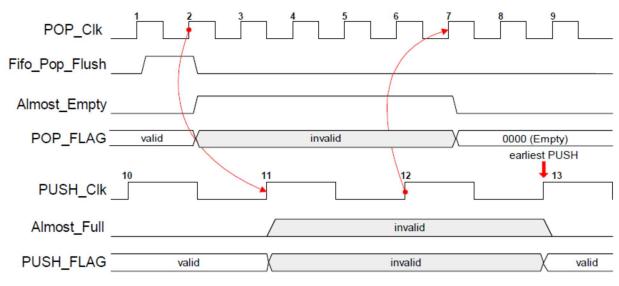

| 27.2.2.3 FIFO Controller                                                             |     |

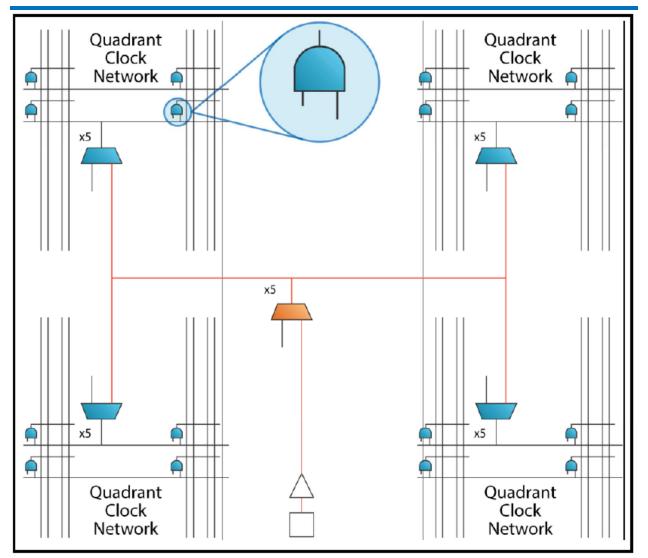

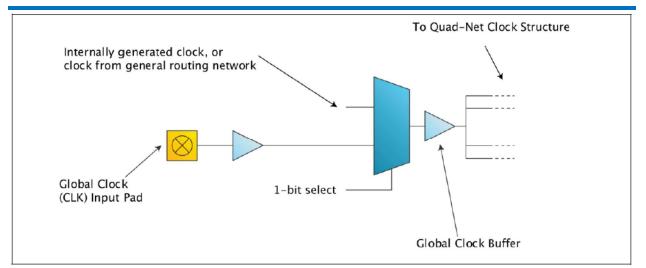

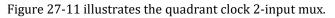

| 27.2.2.4 Distributed Clock Networks                                                  | 270 |

| Global Clocks                                                                        | 270 |

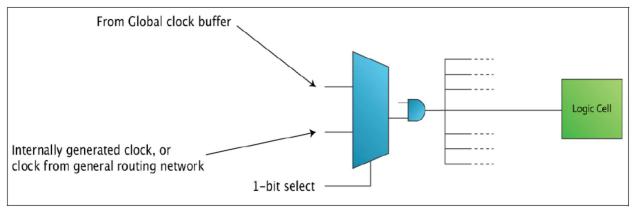

| 27.2.2.5 Configurable Input/Output Signals                                           | 273 |

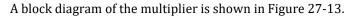

| 27.2.2.6 Multipliers                                                                 |     |

| 27.2.3 Interface to the On-Chip Programmable Logic                                   |     |

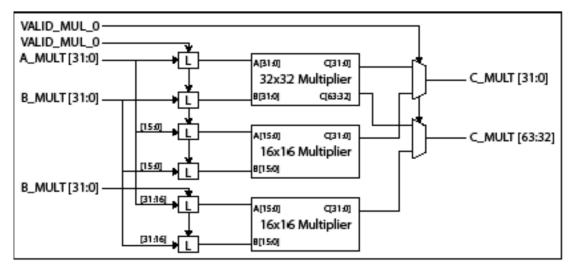

| 27.2.4 S3 Platform Interface                                                         | 275 |

| 27.3 FPGA Use                                                                        | 276 |

| 27.3.1 FPGA Configuration Control                                                    | 276 |

| 27.4 FPGA sub-system registers                                                       | 276 |

|                                                                                      |     |

| Debug                                                                                |     |

| CHAPTER 28. M4-F DEVELOPMENT AND DEBUG SUPPORT ELEMENTS                              |     |

| 28.1 Integrated Configurable Debug                                                   |     |

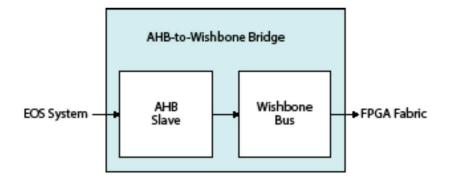

| 28.2 Serial Wire Debug port (SWD)                                                    |     |

| 28.2.1 Debug Configuration                                                           |     |

| 28.2.2 Debug Bootstrap Configuration                                                 |     |

| 28.2.2 Companion/High-Level O/S Host Configuration (Application Processor in System) |     |

| 28.2.4 Host Configuration (the EOS S3 system operating as Host)                      |     |

| 28.2.5 DAP accessible ROM table                                                      |     |

| 28.2.6 AHB-AP                                                                        |     |

| 28.3 Instrumentation Trace Macrocell (ITM)                                           | 279 |

| 28.3.1 ITM Registers                                                                 | 279 |

| 28.4 Data Watchpoint and Trace (DWT)                                                 |     |

| 28.4.1 Registers                                                                     |     |

| 28.5 Flash Patch and Breakpoint Unit (FPB)                                           |     |