## The Rise of Hearables and 8 Challenges the Industry Must Overcome

Implementing Hands-free, Voice Wake-Word Control for TWS Earbuds

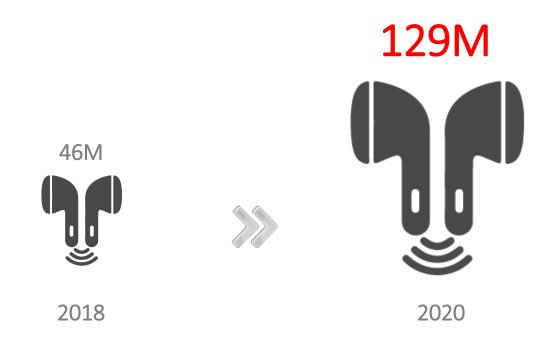

True Wireless Stereo (TWS) earbud headsets have finally become a must-have accessory for the every-day smartphone owner. As shown in figure 1 below, technology market research company Counterpoint reported that 46M units shipped in 2018 and 129M units will hit the market by 2020. Adoption has been widespread across demographic and social lines, teenagers to middle-aged professionals, and will likely continue to broaden over time.

Along with widespread adoption has come the inevitable tide of innovation. TWS headsets had already supported features such as voice calls, music streaming, heart rate monitoring, and fitness tracking, when the introduction of Apple's new AirPods 2 in April of 2019 ushered in arguably one of the most significant new features for both users and developers: true hands-free voice control. As expected, just a couple of weeks after Apple's announcement came rumors that Amazon and Microsoft were working on competing TWS earbud solutions of their own.

Smart headsets with voice control have been around for a while. However, they were mostly of the push-to-talk variety (meaning they wouldn't listen unless a button was pushed first). Some larger over-the-ear headphones were shown at CES this year with true hands-free voice control. Over-the-ear headsets are something of a niche market in this day of pervasive earbuds, but they present an easier job for the designer because they are relatively large and have a proportionally large battery, which supports more CPU processing and better ambient-noise suppression. Multiple design and technical challenges had left the smaller TWS earbud designs stuck with only push-to-talk capability.

Figure 1: TWS Earbud Market Size According to Technology Research Firm Counterpoint

Most of us following the wireless hearables market realized push-to-talk was only a temporary feature. It's hard to find and press a button when you're running or sweaty - It's much easier to just talk. Ideally, you should be able to talk to your devices as you would a friend. Unfortunately, as shown in Figure 2 below, there are significant challenges which make designing and implementing hands-free voice control for TWS earbuds extremely difficult. These include recognizing the voice commands even under adverse conditions, and doing so at an acceptable power level, amount of real estate, and cost for these tiny consumer accessories. These challenges must be overcome quickly, as there is no time for a long design cycle. As almost fashion accessories, earbuds with new features sets come and go on a consumer, not a slower industrial, timeline. Let's explore each of these challenges in a bit more detail.

|          | PERFORMANCE       | 2          | WORK RELIABLY IN NOISY<br>CONDITIONS                   |

|----------|-------------------|------------|--------------------------------------------------------|

|          | POWER             | <b>x</b> 2 | CONSUMERS DEMANDING EVER<br>LONGER BATTERY LIFE        |

| <b>1</b> | MANUFACTURABILITY | ရီစု       | AVAILABLE PCB SPACE VERY<br>LIMITED                    |

|          | TIME-TO-MARKET    | 27:        | CAPITALIZING ON TRENDS MEANS<br>GETTING TO MARKET FAST |

| ş        | COST              | 83         | CONSUMER MARKET VERY COST<br>SENSITIVE                 |

## CHALLENGES

Figure 2: The Challenges Associated with Implementing TWS Earbuds

First and foremost, the voice-activation feature needs to work reliably under a wide range of conditions. When someone says, "Hey Siri", or "Alexa" or "Xioadu Xioadu" the device needs to respond accurately even in noisy environments such as train stations, busy sidewalks or bustling cafes. Long and painful history proves that consumers have no patience with voice-command devices that fail to respond promptly and accurately. And if there's one thing retail stores don't like, it is restocking returned items!

In principle this is a solved problem. The leading noise suppression and voice recognition solutions on the market today provide this quality of user experience. To do so however, they

need specialized DSPs or MCUs, clocked fast enough to offer adequate processing capability. That takes power, which comes at an extreme premium in TWS earbuds, where only the tiniest batteries fit. For example, the Apple Airpod earbud has a 93 mW-hr battery: that is roughly 1% of the battery capacity of an iPhone 7.

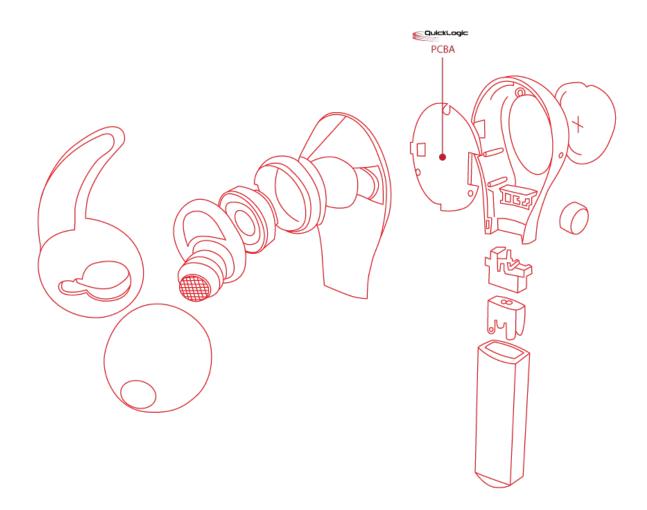

The small battery constrains the power and energy available for the electronics, but that isn't the only limitation. There isn't much space inside a TWS earbud since it must (mostly) fit in the ear with only a small part extending outward (See Figure 3 below.) Every extra pico-acre of space consumed by battery and electronics adds to the mechanical design difficulty of making the device cost-effective and manufacturable in high volume. Those challenges apply to all components of the device including the printed circuit board, flex cabling, and industrial design casing.

Figure 3: TWS Earbuds have Limited Space and Require Thoughtful Mechanical Design

Then there's time-to-market. The consumer business is all about finding popular trends and being able to ride a short-lived wave with a successful product. So the performance, power and manufacturing challenges are compounded by the need to enter the market quickly. That often precludes employing custom chip designs, advanced multi-die packaging, or other technologies with long development cycles.

Last, but never least, is cost. Consumer margins are always tight, and they get tighter as a product category or feature set matures and other vendors enter the market. There's a limited time window for how long a new feature can command a higher price.

Fortunately for designers facing these challenges, there is a SoC designed and optimized specifically for this use case. That SoC is QuickLogic's EOS S3 Voice and Sensor Processing Platform, which provides a flexible, high-bandwidth, and ultra-low power solution for these types of challenging applications.

The EOS S3 is designed specifically for always-on listening for potential voice commands at a fraction of its full operating power. The chip comprises an 80MHz ARM Cortex-M4 core with floating-point unit with 512Kbyte on-chip SRAM, augmented by a number of custom signal-processing accelerators and I/O controllers. See Figure 4 below.

The basic rule for low-power operation is to use the ARM core only when absolutely necessary. With that in mind, voice actuation begins with a set of voice-processing blocks: a continuously running low-power sound detector (LPSD) and a PDM-to-PCM converter that minimize the energy the chip must expend on simply detecting the presence of a sound and preparing it for signal processing. When a potential voice is detected, the M4 is awakened, and the PCM signal is passed to it to run the Key Phrase Detection (KPD) software algorithm. Working together, the blocks achieve 50  $\mu$ A always-on listening for commands, assuming a 3.8 V battery and 85% DC/DC converter efficiency.

Further power reduction is achieved by offloading sensor control and serial I/O functions from the Cortex-M4 to dedicated hardware blocks such as the Flexible Fusion Engine (a 10MHz  $\mu$ DSP) and Sensor Manager. Equally important, an embedded FPGA block allows customer specific-hardware features and I/O expansions. That leaves the M4 to handle operating system and general-purpose task code as necessary.

To enable the fastest possible design cycle, the EOS S3 comes with proven open-source FreeRTOS code and reference designs. The embedded FPGA block allows designers to customize the functions of the chip to their specific use case without waiting for a chip redesign and without having to rely on software to implement time or energy-critical functions. Available wafer-level, chip-scale packaging keeps the EOS S3 within the ultra-tight space limits of earbuds.

| ocks<br>NDC           | ARM<br>Cortex-M4<br>with FPU                                            |                                                                                                                      | SRAM                                                                                                                                                                  |                                                                                                                                     |

|-----------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| lave<br>aster<br>RT   | DMA and<br>FIFOs                                                        |                                                                                                                      | eFPGA                                                                                                                                                                 |                                                                                                                                     |

| Power<br>Ind<br>ector | Flexible                                                                | Sensor<br>Manager                                                                                                    |                                                                                                                                                                       | I <sup>2</sup> C/SPI                                                                                                                |

| PDM<br>to<br>PCM      | Fusion<br>Engine                                                        |                                                                                                                      |                                                                                                                                                                       | l <sup>2</sup>                                                                                                                      |

| PDM                   |                                                                         |                                                                                                                      |                                                                                                                                                                       |                                                                                                                                     |

|                       | ADC<br>lave<br>aster<br>RT<br>Power<br>ind<br>ector<br>PDM<br>to<br>PCM | ocks<br>NDCCortex-M4<br>with FPUlave<br>aster<br>RTDMA and<br>FIFOsPower<br>ind<br>ectorFlexible<br>Fusion<br>Engine | Ocks<br>NDC Cortex-M4<br>with FPU   lave<br>aster<br>RT DMA and<br>FIFOs   ower<br>ector Flexible<br>Fusion<br>Engine   PDM<br>to<br>PCM Flexible<br>Fusion<br>Engine | ocks<br>NDCCortex-M4<br>with FPUSR.lave<br>aster<br>RTDMA and<br>FIFOseFFower<br>ectorFlexible<br>Fusion<br>EngineSensor<br>Manager |

- Sensor Manager Autonomously manages and controls all sensors

- Flexible Fusion Engine<sup>™</sup> (FFE) 10 MHz DSP-like processor supports always-on computational processing at one fourth the power

- eFPGA Enables custom logic functions and I/O expansions

- Voice Processing Hard-coded Low Power Sound Detector (LPSD) and PDM to PCM conversion minimizes audio processing power

- ARM Cortex-M4 with FPU Up to 80 MHz and 512 KB SRAM for general purpose processing and running O/S

- Serial I/O SPI Master/Slave, I<sup>2</sup>C, UART

- System DMA, Integrated RTC, Oscillators, ADC, LDO

*Figure 4: EOS S3 Voice and Sensor Processing Platform Includes an ARM Core and Customizable Blocks*

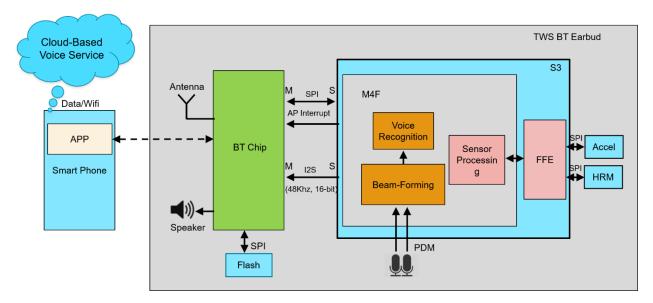

We would argue that with these features, the EOS S3 overcomes the challenges of alwayslistening TWS earbuds. The chip supports accelerometers for bone-conduction detection of speech, simplifying the task of untangling the user's speech from ambient sounds. It then provides highly accurate wake-word detection in real-world noisy environments, using leadingedge noise suppression and voice recognition from Sensory, Nuance, AlSpeech, DSP Concepts and more, running on its M4 core. Figure 5 shows an example block diagram for a TWS Earbud design using the EOS Platform.

Figure 5: Example TWS Earbud Design Block Diagram

To minimize power consumption, the EOS S3 provides hardware-based always-on listening at a 50  $\mu$ W power drain, and can operate voice recognition and sensor management units in ultra-low-power mode while the rest of the system is asleep. In this way we ease the battery size-vs.-life tradeoff for the earbuds.

To reduce time to market, the EOS S3 offers a system of hardware and software already fieldproven inside shipping Bluetooth earbuds with always-on wake-word functionality. The chip is compatible with all major Bluetooth and Bluetooth LE chipsets, and is supported by reference designs.

Manufacturability and cost reduction are greatly enhanced by packing all these functions into a small die in a 2.7 mm by 2.4 mm chip-scale package.

If you're part of a team facing these challenges, and would like to learn more about how QuickLogic can help you, please visit <u>EOS Sensor Processing Platform</u> web page. You can also email us at <u>voice@quicklogic.com</u>.

###