# **QuickLogic EOS S3 Ultra Low Power** multicore MCU datasheet

**Version 3.3f**

### **Contact Information**

E-mail: info@quicklogic.com

Sales: America-sales@quicklogic.com

Europe-sales@quicklogic.com

Asia-sales@quicklogic.com

Japan-sales@quicklogic.com

Korea-sales@quicklogic.com

Support: www.quicklogic.com/support

Internet: www.quicklogic.com

### **Notice of Disclaimer**

QuickLogic is providing this design, product or intellectual property, 'as is'. By providing the design, product or intellectual property as one possible implementation of your desired system-level feature, application, or standard, QuickLogic makes no representation that this implementation is free from any claims of infringement and any implied warranties of merchantability or fitness for a particular purpose. You are responsible for obtaining any rights you may require for your system implementation. QuickLogic shall not be liable for any damages arising out of or in connection with the use of the design, product or intellectual property including liability for lost profit, business interruption, or any other damages whatsoever. QuickLogic products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use QuickLogic products in these types of equipment or applications.

QuickLogic does not assume any liability for errors which may appear in this document. However, QuickLogic attempts to notify customers of such errors. QuickLogic retains the right to make changes to either the documentation, specification, or product without notice. Verify with QuickLogic that you have the latest specifications before finalizing a product design.

### **Copyright and Trademark Information**

Copyright © 2020 QuickLogic Corporation. All Rights Reserved.

The information contained in this document and the accompanying software programs is protected by copyright. All rights are reserved by QuickLogic Corporation. QuickLogic Corporation reserves the right to modify this document without any obligation to notify any person or entity of such revision. Copying, duplicating, selling, or otherwise distributing any part of this product without the prior written consent of an authorized representative of QuickLogic is prohibited.

QuickLogic is a registered trademark, and the QuickLogic logo and ArcticLink are trademarks of QuickLogic. Other trademarks are the property of their respective companies.

### **EOS S3 Ordering Part Numbers**

| Part Number                          | Device Description                                                              |

|--------------------------------------|---------------------------------------------------------------------------------|

| EOS3FF512-PDN64<br>EOS3FF512-WRN42   | EOS S3 Ultra Low Power MCU + eFPGA with Open Source SW                          |

| EOS3FLF512-PDN64<br>EOS3FLF512-WRN42 | EOS S3 Ultra Low Power MCU + LPSD + eFPGA with Open Source SW                   |

| EOS3C512-PDN64<br>EOS3C512-WRN42     | EOS S3 Ultra Low Power Sensor Processor + Flexible Fusion Engine                |

| EOS3CF512-PDN64<br>EOS3CF512-WRN42   | EOS S3 Ultra Low Power Sensor Processor + Flexible Fusion Engine + eFPGA        |

| EOS3CL512-PDN64<br>EOS3CL512-WRN42   | EOS S3 Ultra Low Power Sensor Processor + Flexible Fusion Engine + LPSD         |

| EOS3CLF512-PDN64<br>EOS3CLF512-WRN42 | EOS S3 Ultra Low Power Sensor Processor + Flexible Fusion Engine + LPSD + eFPGA |

Note: Not all cores (FFE, eFPGA, LPSD) are available in all devices. Refer to the above table for the correct part number.

### **Contents**

| QuickLogic EOS S3 Ultra Low Power multicore MCU Platform Highlights | 13 |

|---------------------------------------------------------------------|----|

| 1. Functional Overview                                              | 15 |

| 1.1. EOS S3 Ultra Low Power multicore MCU Platform Architecture     | 15 |

| 2. M4-F Processor Subsystem                                         | 20 |

| 2.1. Subsystem Overview                                             | 20 |

| 2.1.1. System-Level Interface                                       | 21 |

| 2.1.2. Integrated Configurable Debug                                | 21 |

| 2.1.3. M4-F and Core Peripherals                                    | 21 |

| 2.1.4. Embedded SRAM                                                | 22 |

| 2.1.5. Development Support (Serial Wire Interface)                  | 23 |

| 2.1.6. Debugger Bootstrap Configurations                            | 24 |

| 3. Sensor Processing Subsystem                                      | 25 |

| 3.1. Overview                                                       |    |

| 3.2. Flexible Fusion Engine                                         | 26 |

| 3.2.1. µDSP-Like Processor                                          | 26 |

| 3.2.2. Instruction Memory                                           | 27 |

| 3.2.3. Data Memory                                                  | 27 |

| 3.3. Sensor Manager                                                 | 27 |

| 3.3.1. Microcontroller Unit                                         | 28 |

| 3.3.2. Instruction and Data Memory                                  | 28 |

| 3.4. I <sup>2</sup> C Master                                        | 29 |

| 3.4.1. System Configuration                                         | 30 |

| 3.4.2. I <sup>2</sup> C Protocol                                    | 30 |

| 3.4.3. START Signal                                                 |    |

| 3.4.4. Slave Address Transfer                                       | 32 |

| 3.4.5. Data Transfer                                                | 32 |

| 3.4.6. STOP Signal                                                  | 32 |

| 3.4.7. Arbitration                                                  | 32 |

| 3.4.8. I <sup>2</sup> C Core Architecture                           | 32 |

| 3.4.9. Clock Generator                                              | 33 |

| 3.4.10. Byte Command Controller                                     | 33 |

| 3.4.11. Bit Command Controller                                      | 34 |

| 3.4.12. Data I/O Shift Register                                     | 34 |

| 3.5. Serial Peripheral Interface (SPI)                              | 34 |

| 3.5.1. SPI Master for System Support                                | 35 |

| 3.5.2. SPI Master for System Support Features                       | 35 |

| 3.5.3. Configuration Logic                                          | 36 |

| 3.5.4. SPI Master for Sensor Processing Subsystem Support           | 37 |

| 3.5.5. SPI Slave                               | 37  |

|------------------------------------------------|-----|

| 3.5.6. SPI Interface Protocol                  | 39  |

| 3.5.7. Basic Read/Write Transfers              | 39  |

| 3.5.8. Device ID Read                          | 40  |

| 3.5.9. Transfer Types                          | 40  |

| 3.5.10. Transfers to TLC Local Registers       | 41  |

| 3.5.11. Transfers from Packet FIFOs            | 41  |

| 3.5.12. Transfers to M4-F Memory Address Space | 41  |

| 3.5.13. Basic AHB Transfer Restrictions        | 41  |

| 3.5.14. SPI Write Cycle                        | 43  |

| 3.5.15. SPI Read Cycle                         | 43  |

| 3.5.16. SPI Multiple Read Cycle                | 43  |

| 3.5.17. SPI 3-Wire Configuration               | 44  |

| 3.5.18. SPI Corner Cases                       | 44  |

| 3.5.19. Transmission Format                    |     |

| 3.5.20. Clock Phase and Polarity Controls      | 46  |

| 3.6. AHB Master Bridge                         | 50  |

| 3.7. Control Registers                         | 50  |

| 3.8. Packet FIFO                               | 50  |

| 3.9. On-Chip Programmable Logic                | 50  |

| A Walter Out and ton                           | F.4 |

| 4. Voice Subsystem                             |     |

| 4.1. PDM Microphone                            |     |

| 4.2. I <sup>2</sup> S Microphones              | 51  |

| 4.3. Low Power Sound Detect Support            | 52  |

| 4.4. PDM Slave Port for External Codec         | 52  |

| 4.5, DMA and AHB Master Port                   | 52  |

| 4.6, APB Slave Port                            |     |

|                                                |     |

| 4.7. I <sup>2</sup> S Slave Port               | 52  |

| 5. Timing                                      | 54  |

|                                                |     |

| 5.1. I <sup>2</sup> C Master AC Timing         |     |

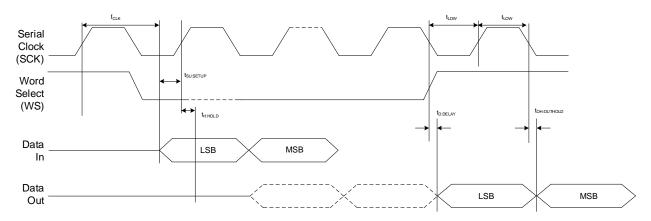

| 5.2. I <sup>2</sup> S Timing                   | 54  |

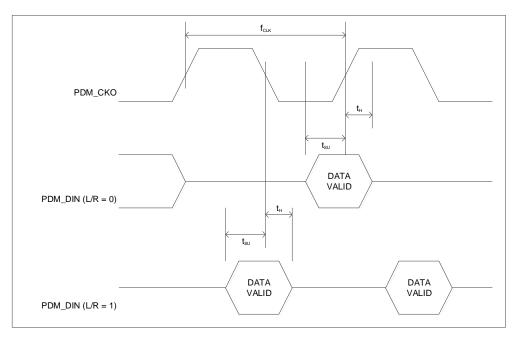

| 5.3. PDM Microphone Timing                     |     |

| 5.4. SPI Timing                                | 56  |

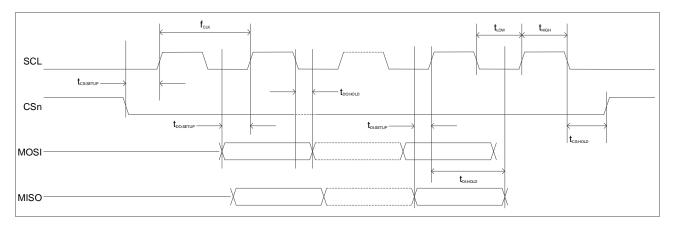

| 5.4.1. SPI Master                              | 56  |

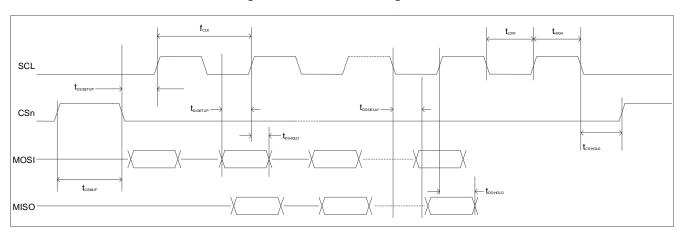

| 5.4.2. SPI Slave                               | 58  |

|                                                |     |

| 6. On-Chip Programmable Logic                  |     |

| 6.1. Functional Description                    |     |

| 6.1.1. Logic Cell                              |     |

| 6.2. RAM/FIFO                                  | 61  |

| 6.2.1. FIFO Controller                                               | 61    |

|----------------------------------------------------------------------|-------|

| 6.2.2. Configurable Input/Output Signals                             | 61    |

| 6.2.3. Multipliers                                                   | 62    |

| 6.3. Interface to the On-Chip Programmable Logic                     | 64    |

| 6.3.1. EOS S3 Platform Interface                                     | 64    |

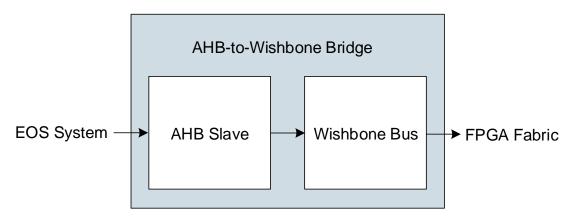

| 6.3.2. AHB-To-Wishbone Bridge                                        | 64    |

| 6.3.3. SDMA Interface                                                |       |

| 6.3.4. Interrupt Interface                                           |       |

| 6.3.5. Sensor Processing Subsystem Interface                         |       |

| 6.3.6. Packet FIFO Interface                                         | 65    |

| 7. Power Management                                                  | 66    |

| 7.1. Power Supply Modes and Schemes                                  | 66    |

| 7.2. SRAM Power Domains                                              | 67    |

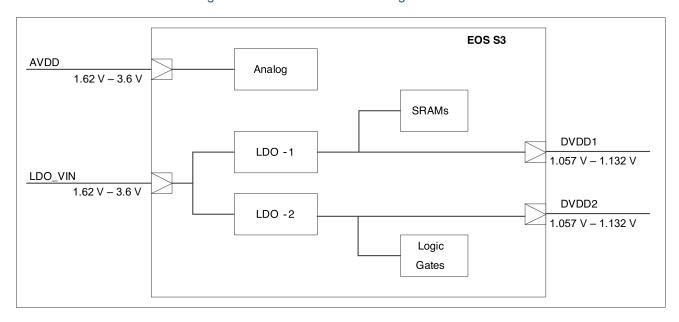

| 7.3. Low Dropout Regulators                                          | 68    |

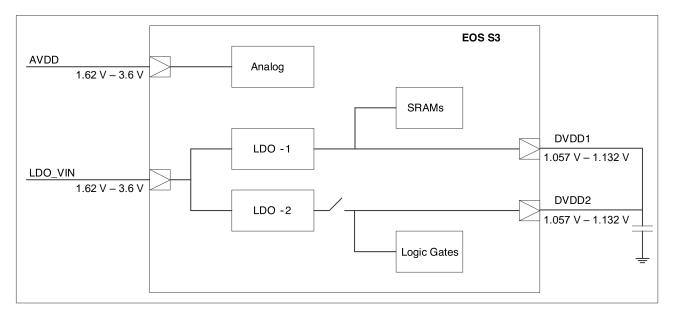

| 7.3.1. Use Case 1: Dual Voltage Rail Supplied by On-Chip LDOs        | 68    |

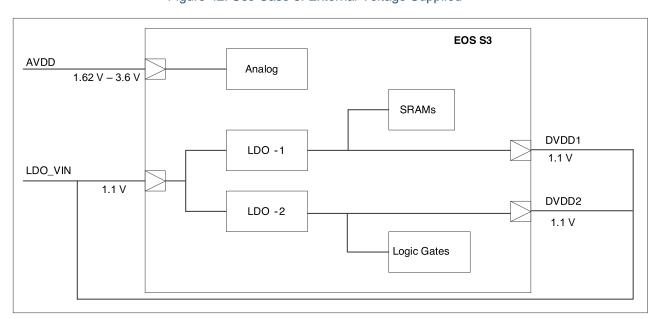

| 7.3.2. Use Case 2: Single Voltage Rail Supplied by Single On-Chip LD | OOs68 |

| 7.3.3. Use Case 3: External Voltage Supplied                         | 69    |

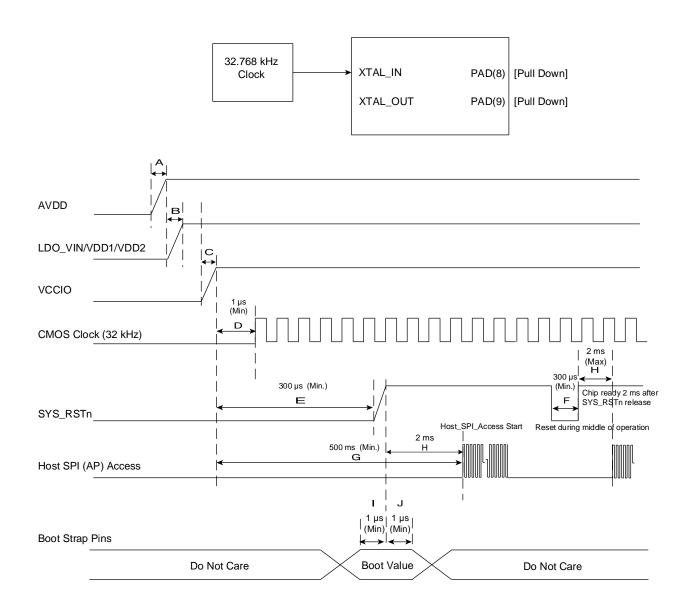

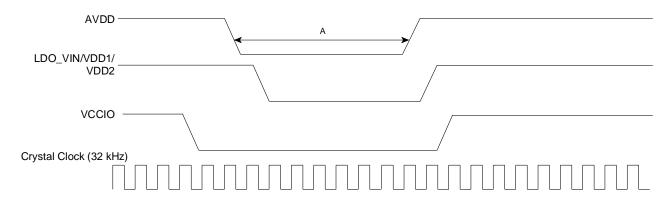

| 7.4. Power-On Sequence of CMOS Clock                                 | 70    |

| 7.5. Power-Down Sequence of CMOS Clock                               | 73    |

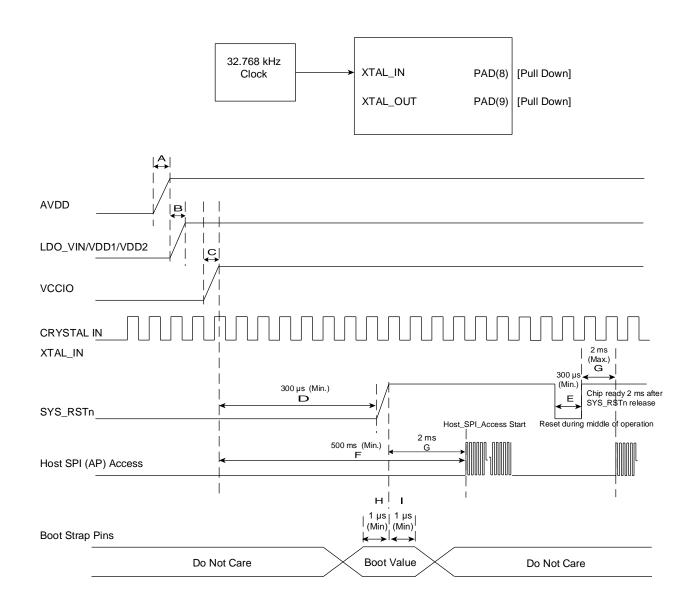

| 7.6. Power-On Sequence of Crystal Clock                              | 75    |

| 7.7. Power-Down Sequence of Crystal Clock                            | 77    |

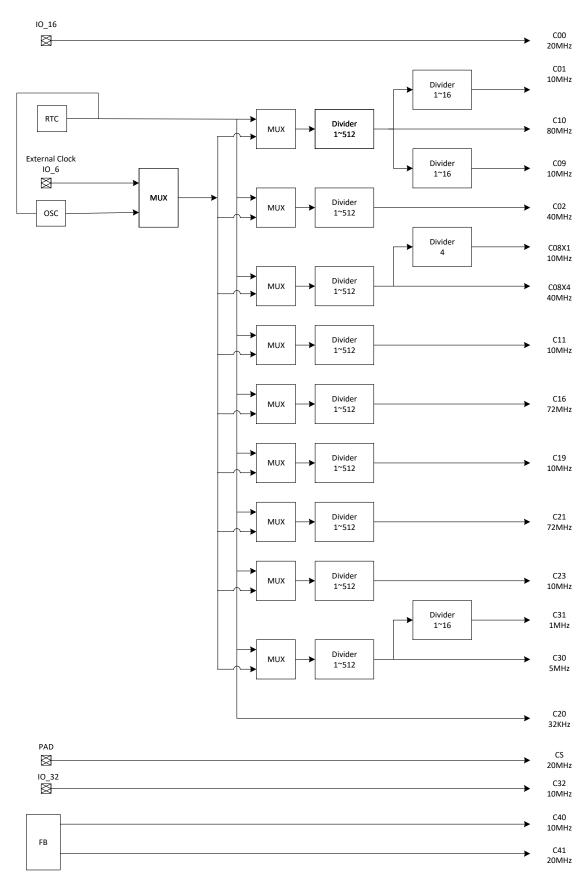

| 7.8. Clocks and Resets                                               | 78    |

| 7.8.1. Clocks                                                        | 78    |

| 7.8.2. Resets                                                        | 81    |

| 8. Other EOS S3 Platform Features                                    | 82    |

| 8.1. Multi-Function Inputs/Outputs (IOs)                             | 82    |

| 8.2. General Purpose Inputs/Outputs (GPIOs)                          | 82    |

| 8.3. Fabric Inputs/Outputs (FBIOs)                                   | 82    |

| 8.4. Interrupts                                                      |       |

| 8.4.1. Interrupt Structure                                           | 82    |

| 8.4.2. Interrupt Sources                                             | 83    |

| 8.4.3. M4-F Wake-Up Events                                           | 84    |

| 8.5. Bootstrap Modes                                                 | 85    |

| 8.6. M4-F Serial Wire Debug Port Configuration                       | 85    |

| 8.6.1. Internal/External HSO Configuration                           | 86    |

| 8.6.2. SWD Debugger Present Configuration                            | 86    |

| 8.6.3. AP/Wearable Mode Configuration                                | 86    |

| 9. Other Peripherals                                                 | 87    |

| 9.1. Packet FIFO                                                     |       |

| 9.1.1. FIFO_8K                                                       | 88    |

| 9.1.2. FIFO_0, FIFO_1, FIFO_2                                        | 88    |

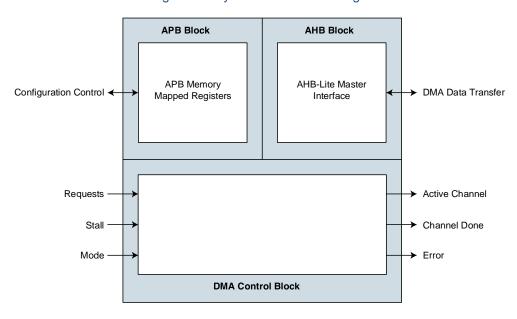

| 9.2. System DMA                                         | 89  |

|---------------------------------------------------------|-----|

| 9.2.1. Functional Description                           | 89  |

| 9.2.2. SDMA Configurations                              | 91  |

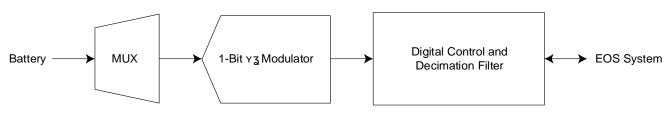

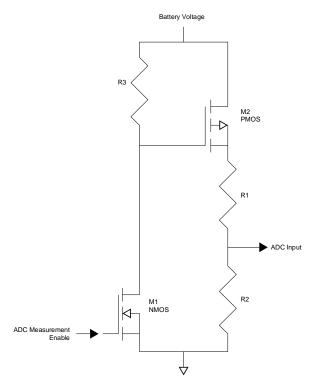

| 9.3. Analog-to-Digital Converter                        | 91  |

| 9.3.1. Overview                                         | 91  |

| 9.3.2. Functional Description                           | 92  |

| 9.3.3. Electrical Characteristics                       | 92  |

| 9.3.4. PCB Layout Recommendations                       |     |

| 9.3.5. Example Application                              |     |

| 9.4. Universal Asynchronous Receiver Transmitter (UART) |     |

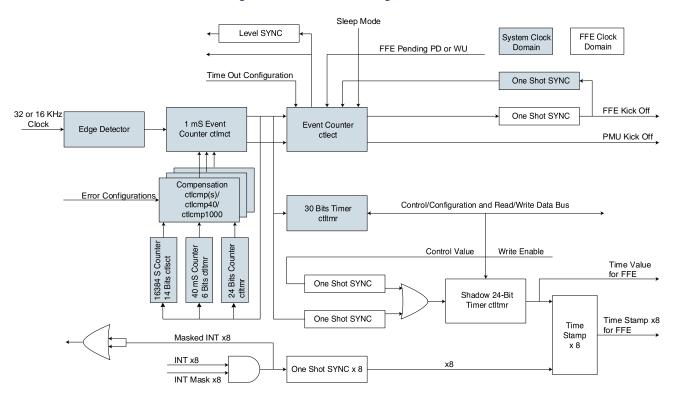

| 9.5. Timer and Counters                                 |     |

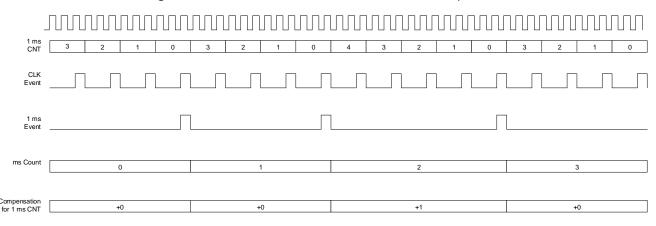

| 9.5.1. 1 ms Event Counter                               |     |

| 9.5.2. Error Correction for 1 mS Event Counter          |     |

| 9.5.3. Timeout Event Counter                            |     |

| 9.5.4. 30-Bit Counter                                   |     |

| 9.5.5. Time Stamp Counters                              |     |

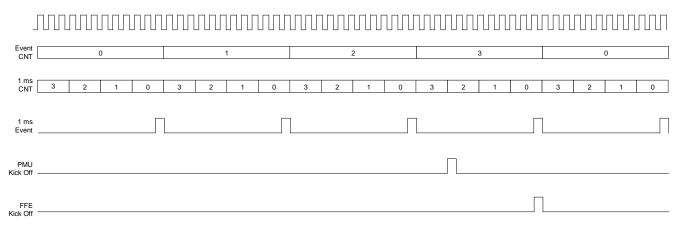

| 9.5.6. PMU and FFE Wakeup                               | 96  |

| 10. Device Characteristics                              | 98  |

| 10.1. Pinout and Pin Description                        |     |

| 10.2. I/O State                                         |     |

|                                                         |     |

| 11. Electrical Specifications                           | 105 |

| 11.1. DC Characteristics                                |     |

| 11.2. Output Drive Current                              | 107 |

| 11.3. Clock and Oscillator Characteristics              |     |

| 11.4. Output Rise/Fall Time                             | 108 |

| 11.4.1. Output Rise/Fall Time (VCCIO = 1.8V)            |     |

| 11.4.2. Output Rise/Fall Time (VCCIO = 2.5V)            |     |

| 11.4.3. Output Rise/Fall Time (VCCIO = 3.3V)            |     |

| 11.5. Power Consumption                                 | 110 |

| 12. Application Examples                                | 112 |

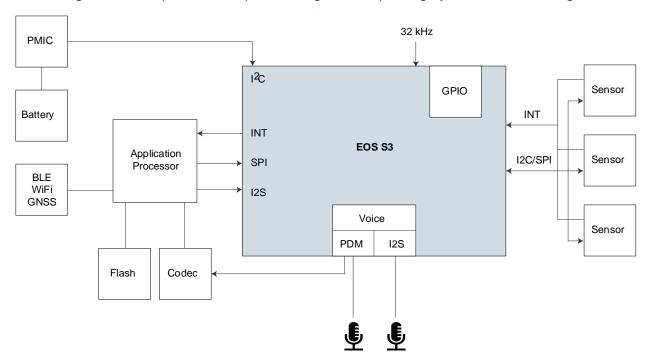

| 12.1. Smartphone or High-Level O/S Wearable Design      |     |

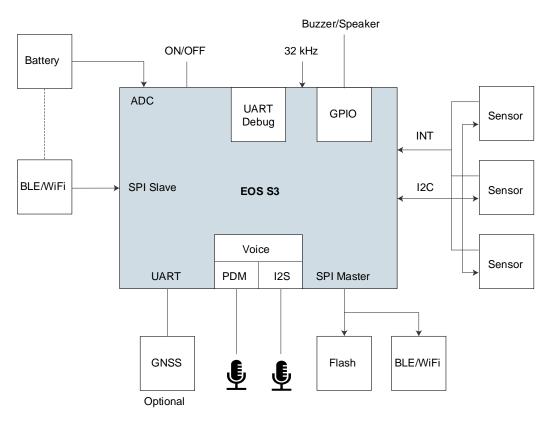

| 12.2. Real-Time Operating System Wearable Design        |     |

| 12.2. Roar Fillio Operating Cystem Wearable Design      | 112 |

| 13. Package Information                                 |     |

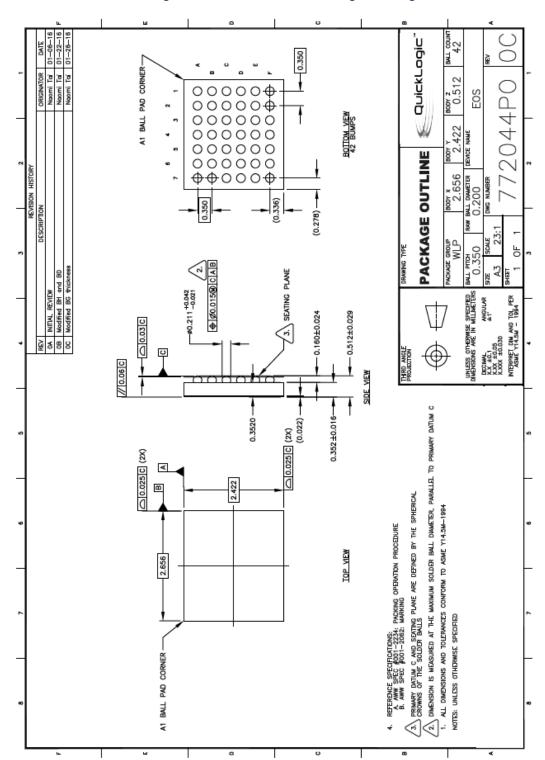

| 13.1. 42-Ball WLCSP Package Drawing                     | 114 |

| 13.2. 64-Ball BGA Package Drawing                       | 115 |

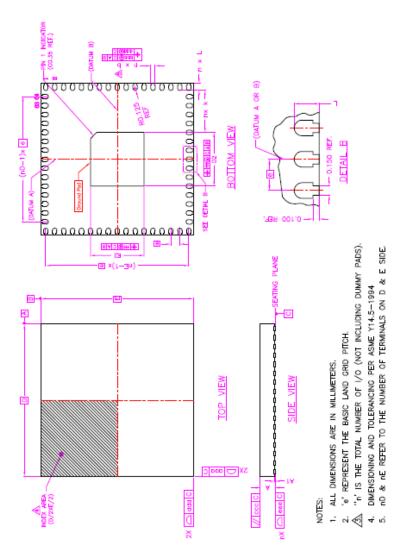

| 13.3. 64-Pin QFN Package Drawing                        | 116 |

| 14. Soldering Information                               | 117 |

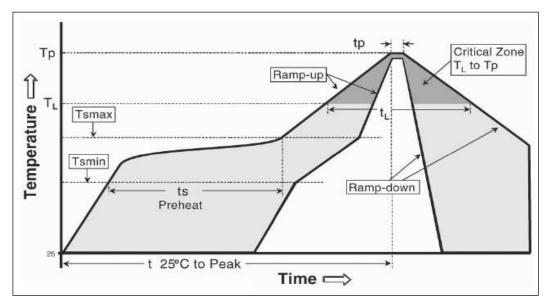

| 14.1. Reflow Profile                                    |     |

| 14.2. Package Thermal Characteristics                   |     |

| TIET COMAGO THOMAS CHARACTORIOS                         | 110 |

| Quickl oaic | FOS S3 Ulf | a Low Powe  | r multicore MCL | I datasheet - | Version 3    | .3e |

|-------------|------------|-------------|-----------------|---------------|--------------|-----|

| Quion Logic |            | a Low I one |                 | uutusiicet    | V CI SIOII S |     |

| 27-   | 120 |

|-------|-----|

| ~ / - | 123 |

15. Revision History......119

©2020 QuickLogic Corporation

### **Figures**

| Figure 1: EOS S3 Ultra Low Power multicore MCU Platform Architecture             | 15 |

|----------------------------------------------------------------------------------|----|

| Figure 2: EOS S3 Ultra Low Power multicore MCU Platform Block Diagram            | 19 |

| Figure 3: Cortex M4-F Block Diagram                                              |    |

| Figure 4: Recommended External Debugger Connection for ARM DS Debugger           | 24 |

| Figure 5: Sensor Processing Subsystem Block Diagram                              | 25 |

| Figure 6: FFE Architecture                                                       |    |

| Figure 7: Sensor Manager Architecture                                            | 28 |

| Figure 8: I2C Modules within the EOS S3 Platform                                 | 29 |

| Figure 9: I <sup>2</sup> C Protocol Example                                      | 30 |

| Figure 10: I <sup>2</sup> C Block Diagram                                        |    |

| Figure 11: I <sup>2</sup> C Bit Command Sequences                                | 34 |

| Figure 12: On-Chip Programmable Logic IP Access to SPI Master for System Support |    |

| Figure 13: SPI Interface used for Sensor Processing Subsystem Support            |    |

| Figure 14: SPI Slave Block Diagram                                               |    |

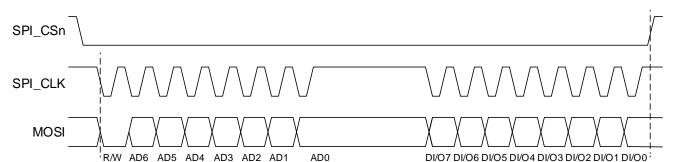

| Figure 15: SPI Slave Protocol Diagram                                            |    |

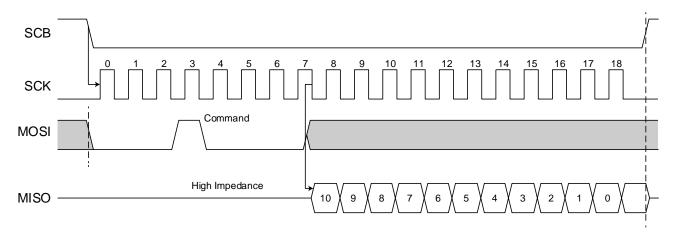

| Figure 16: SPI Slave Device ID Read Protocol                                     |    |

| Figure 17: SPI Master Burst Write Sequence                                       |    |

| Figure 18: Example Burst Read Sequence                                           |    |

| Figure 19: Basic SPI Write Operation (Mode 11)                                   |    |

| Figure 20: Basic SPI Read Operation (Mode 11)                                    |    |

| Figure 21: SPI Multiple Read Operation (Mode 11)                                 |    |

| Figure 22: 3-Wire Basic SPI Read/Write Sequence (Mode 11)                        |    |

| Figure 23: muRata Command and 11-bit SPI Acceleration Data Read Sequence         |    |

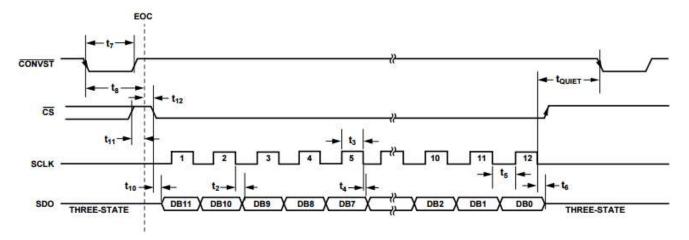

| Figure 24: AD7091 SPI Transfer Sequence                                          |    |

| Figure 25: SPI Block Diagram                                                     |    |

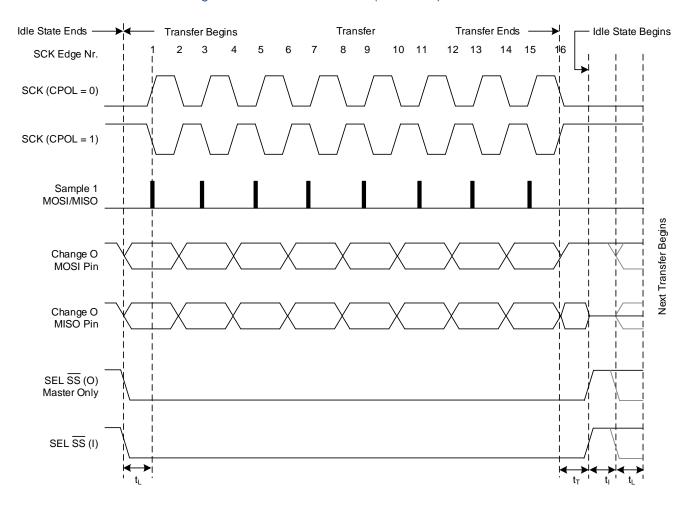

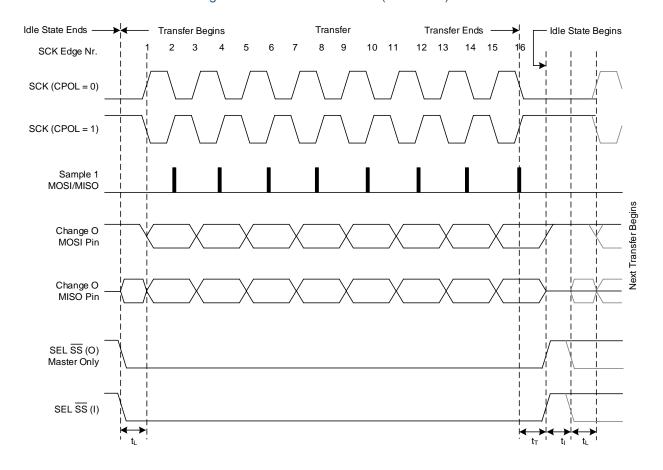

| Figure 26: SPI Clock Format 0 (CPHA = 0)                                         |    |

| Figure 27: SPI Clock Format 1 (CPHA = 1)                                         |    |

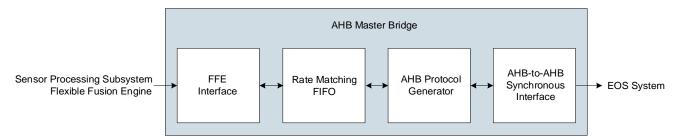

| Figure 28: FFE AHB Master Bridge Block Diagram                                   |    |

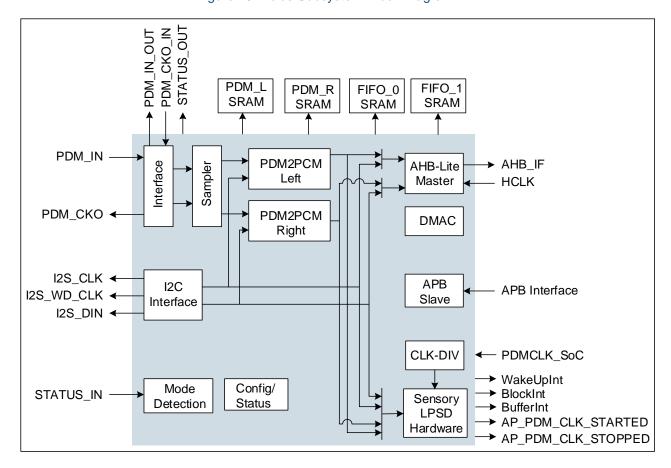

| Figure 29: Voice Subsystem Block Diagram                                         |    |

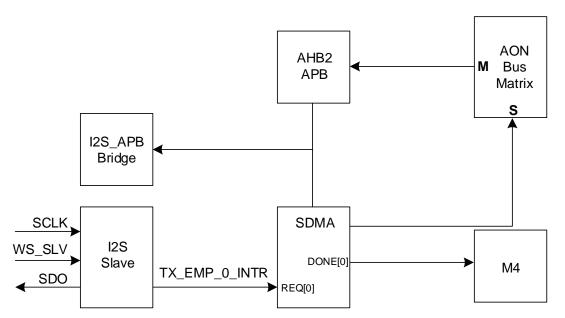

| Figure 30: I <sup>2</sup> S Slave Port                                           |    |

| Figure 31: I <sup>2</sup> C Master AC Timing                                     |    |

| Figure 32: I <sup>2</sup> S Timing Waveform                                      |    |

| Figure 33: PDM Microphone Timing                                                 |    |

| Figure 34: SPI Master AC Timing                                                  |    |

|                                                                                  |    |

| Figure 35: SPI Slave Timing                                                      |    |

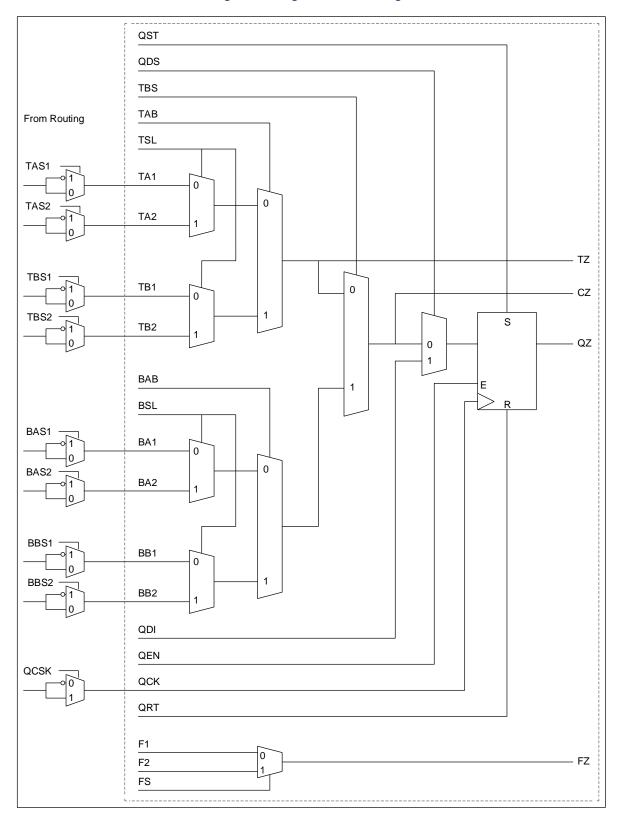

| Figure 36: Logic Cell Block Diagram                                              |    |

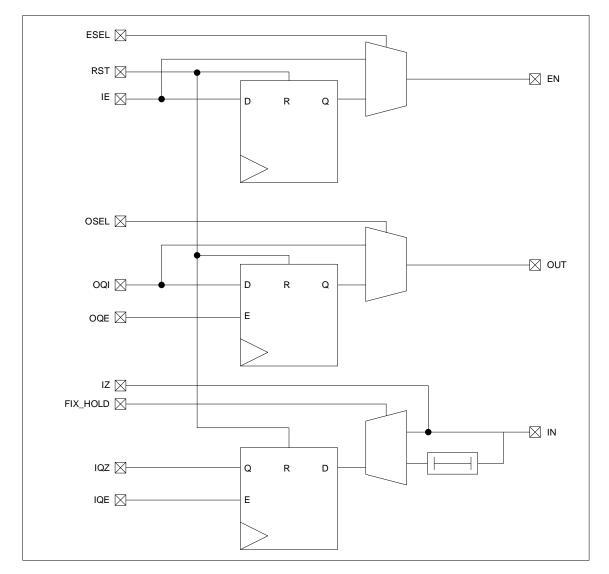

| Figure 37: On-Chip Programmable Logic Configurable Input/Output                  |    |

| Figure 38: On-Chip Programmable Logic Multiplier                                 |    |

| Figure 39: AHB-to-Wishbone Bridge<br>Figure 40: Use Case 1: Dual Voltage Rail    |    |

|                                                                                  |    |

| Figure 41: Use Case 2: Single Voltage Rail                                       |    |

| Figure 42: Use Case 3: External Voltage Supplied                                 |    |

| Figure 43: Power-On Sequence of CMOS Clock                                       |    |

| Figure 44: Current Measurement Scheme with External Power Supplies               |    |

| Figure 45: Power-Down Sequence of CMOS Clock                                     |    |

| Figure 46: Power-On Sequence of Crystal Clock                                    |    |

| Figure 47: Power-Down Sequence of Crystal Clock<br>Figure 48: Clock Tree         |    |

| FIUUIE 40. VIUUK TIEE                                                            | o∪ |

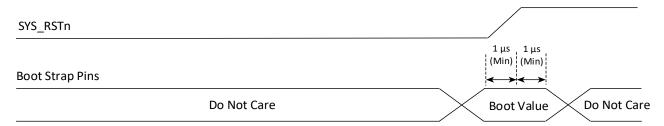

| Figure 49: Bootstrap Timing                                                       | 85  |

|-----------------------------------------------------------------------------------|-----|

| Figure 50: PKFB Block Diagram                                                     |     |

| Figure 51: System DMA Block Diagram                                               | 89  |

| Figure 52: System DMA Interface                                                   | 90  |

| Figure 53: ADC Block Diagram                                                      | 91  |

| Figure 54: Example Voltage Divider Circuit                                        | 93  |

| Figure 55: Timer Block Diagram                                                    | 95  |

| Figure 56: 1 ms Count and 1 ms Counter Relationship                               | 96  |

| Figure 57: PMU and FFE Timing Waveform                                            | 97  |

| Figure 58: Example of a Smartphone or High-Level Operating System Wearable Design | 112 |

| Figure 59: Example of a Real-Time Operating System Wearable Design                | 113 |

| Figure 60: 42-Ball WLCSP Package Drawing                                          | 114 |

| Figure 61: 64-Ball BGA Package Drawing                                            |     |

| Figure 62: 64-Pin QFN Package Drawing                                             |     |

| Figure 63: Pb-Free Component Preconditioning Reflow Profile                       |     |

### **Tables**

| Table 1: EOS S3 Platform Supported Features                                                              | . 17 |

|----------------------------------------------------------------------------------------------------------|------|

| Table 2: I <sup>2</sup> C Master AC Timing                                                               | . 54 |

| Table 3: I <sup>2</sup> S Timing                                                                         | . 55 |

| Table 4: PDM Microphone Timing                                                                           |      |

| Table 5: SPI Master Timing                                                                               | . 57 |

| Table 6: SPI Slave Timing                                                                                | . 58 |

| Table 7: On-Chip Programmable Logic Major Features                                                       | . 59 |

| Table 8: FPGA performance                                                                                | . 59 |

| Table 9: Power Domains                                                                                   |      |

| Table 10: Memory Domains                                                                                 |      |

| Table 11: LDO Regulators                                                                                 |      |

| Table 12: Power-On Sequence Timing Parameters                                                            |      |

| Table 13: Current Measurements for Power-On Sequence <sup>a</sup>                                        |      |

| Table 14: Current Measurements for Power-On Sequence <sup>a</sup>                                        |      |

| Table 15: Power-Down Sequencing Timing Parameters                                                        | . 73 |

| Table 16: Current Measurements for Power-Down <sup>a</sup>                                               | . 73 |

| Table 17: LDO Mode Typical Inrush Current <sup>a</sup>                                                   | . 74 |

| Table 18: LDO Bypass Mode Typical Inrush Current                                                         |      |

| Table 19: Maximum Supply Power Consumption                                                               | . 74 |

| Table 20: Power-On Sequence Timing Parameters                                                            |      |

| Table 21: Power-Down Duration Time for AVDD                                                              |      |

| Table 22: Clocks Listing                                                                                 |      |

| Table 23: Bootstrap Timing During Power-On Sequence                                                      |      |

| Table 24: M4-F Serial Wire Debug Port Bootstrap Configuration                                            |      |

| Table 25: Internal/External HSO Configuration                                                            |      |

| Table 26: SWD Debugger Present Configuration                                                             |      |

| Table 27: AP/Wearable Mode Configuration                                                                 |      |

| Table 28: Packet FIFO Instances                                                                          |      |

| Table 29: SDMA Channel Assignment                                                                        |      |

| Table 30: ADC Electrical Characteristics  Table 31: EOS S3 Ultra Low Power multicore MCU Platform Pinout |      |

|                                                                                                          |      |

| Table 32: I/O State Table 33: Absolute Maximum Ratings                                                   |      |

| Table 33: Absolute Maximum Ratings                                                                       |      |

| Table 34: Recommended Operating Range                                                                    |      |

| ·                                                                                                        |      |

| Table 36: DC Input and Output Levels <sup>a</sup>                                                        |      |

| Table 37: Output Drive Current (VDD = 1.8V) in mA                                                        |      |

| Table 38: Output Drive Current (VDD = 2.5V) in mA                                                        |      |

| Table 39: Output Drive Current (VDD = 3.3V) in mA                                                        |      |

| Table 40: Clock and Oscillator Characteristics <sup>a,b</sup>                                            |      |

| Table 41: Output Rise/Fall Time (SR = 1, VCCIO = 1.8 V)                                                  | 108  |

| Table 42: Output Rise/Fall Time (SR = 0, VCCIO = 1.8V)                                                   |      |

| Table 43: Output Rise/Fall Time (SR = 1, VCCIO = 2.5 V)                                                  |      |

| Table 44: Output Rise/Fall Time (SR = 0, VCCIO = 2.5 V)                                                  |      |

| Table 45: Output Rise/Fall Time (SR = 1, VCCIO = 3.3V)                                                   |      |

| Table 46: Output Rise/Fall Time (SR = 0, VCCIO = 3.3V)                                                   |      |

| Table 47: Shutdown Current <sup>a</sup>                                                                  | 110  |

| Table 48: Standby Current <sup>a</sup>                                     | 111 |

|----------------------------------------------------------------------------|-----|

| Table 49: CoreMark Current Values                                          | 111 |

| Table 50: EOS S3 Power Measurements                                        | 111 |

| Table 51: Pb-Free Component Preconditioning Reflow Profile <sup>a, b</sup> | 117 |

| Table 52: Package Thermal Characteristics                                  | 118 |

©2020 QuickLogic Corporation

## QuickLogic EOS S3 Ultra Low Power multicore MCU Platform Highlights

### Multi-Core, Ultra Low Power Sensor and Audio Processing Platform Enabling Always-On, Always-Aware Application

### **Multi-Core Design**

- Ultra-low power μDSP-like Flexible Fusion Engine (FFE) for always-on, real-time sensor fusion algorithms, an ARM<sup>®</sup> Cortex<sup>®</sup> M4-F floating point processor for general purpose processing, and on-chip programmable logic for flexibility and integration of additional logic functions to a single device

- Multiple, concurrent cores enable algorithm partitioning capability to achieve the most power and computationally efficient sensor processing system-on-a-chip (SoC) in the market

#### Cortex M4-F Processor

- Up to 80 MHz operating frequency

- Up to 512 KB SRAM with multiple power modes, including deep sleep (128 KB of this memory can be used for HiFi sensor batching)

- Ideal for computationally intensive sensor processing algorithms (continuous heart rate monitor, indoor navigation, always-on voice recognition, etc.)

### Third-Generation Flexible Fusion Engine

- Up to 10 MHz operating frequency

- 50 KB control memory

- 16 KB data memory

- µDSP-like architecture for efficient mathematical computations

- Ideal for always-on, real-time sensor fusion algorithms (such as pedometer, activity classification, gesture recognition, and others)

- initialization and sampling of sensors through hard-wire I2C or configurable I2C/SPI interface

- Dramatically lowers the power consumption associated with sensor data acquisition

### **Communication Manager**

Communicates with host applications processor through the SPI Slave interface of up to 20 MHz

### **Dedicated Voice Support**

- Audio support for Pulse Density Modulation (PDM) or I2S microphones

- Optional hardware PDM bypass path to forward microphone data to application processor or Voice CODEC

- Dedicated logic for PDM to Pulse Code Modulation (PCM) conversion

- Dedicated hard logic integration of Sensory Low Power Sound Detect (LPSD) for on-chip voice recognition

### **On-Chip Programmable Logic**

- 2,400 effective logic cells with 64 Kbits of RAM available

- Eight RAM FIFO controllers

- Provides capability to add logic functions or augment existing logic functions

### **Operating System Support**

Android 6.0 compliant

### Sensor Manager

- 1.5 KB x 18-bit memory

- Completely autonomous (zero load on M4-F)

#### **Additional Features**

- On-device circuit to support 32.768 kHz clock or crystal oscillator

- Thirty-one different power islands for granular management of system power

- Power Management Unit (PMU) for minimizing power in all conditions (idle, deep sleep, and shut down)

- SPI Master, SPI Slave, I2S Master, I2S Slave, and I2C interfaces

- 12-bit  $\Sigma \Delta$  Analog-to-Digital Converter (ADC)

- 2-pin Serial Wire Debug (SWD) port

- System DMA engine for efficient data movement

- Dual Low-Dropout (LDO) regulators for onchip voltage regulation

### 1. Functional Overview

The QuickLogic® S3 platform is a multi-core, ultra-low power sensor processing system designed for mobile market applications such as smartphone, wearable, and Internet of Things (IoT) devices. The core of the EOS S3 platform is its proprietary µDSP-like Flexible Fusion Engine (FFE). To complement the FFE, the EOS S3 platform also includes a Cortex M4-F subsystem that enables higher level, general purpose processing.

This multi-core architecture enables smartphone application processors to offload real-time, always-on sensor computational requirements to the EOS S3 platform. The multi-core approach and multiple power islands allow the EOS S3 platform to process sensor data and run sensor fusion algorithms in the most efficient manner possible for both processing and power.

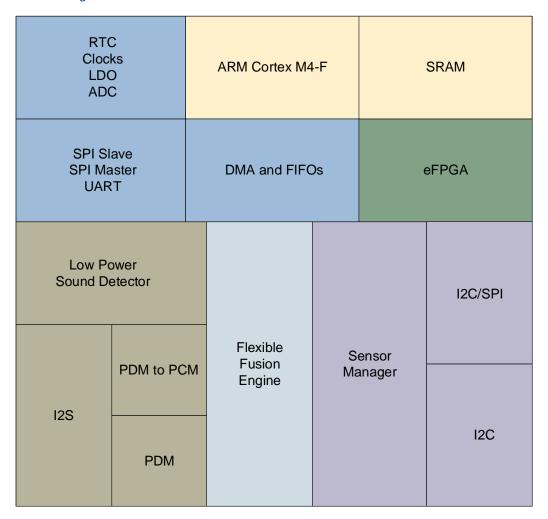

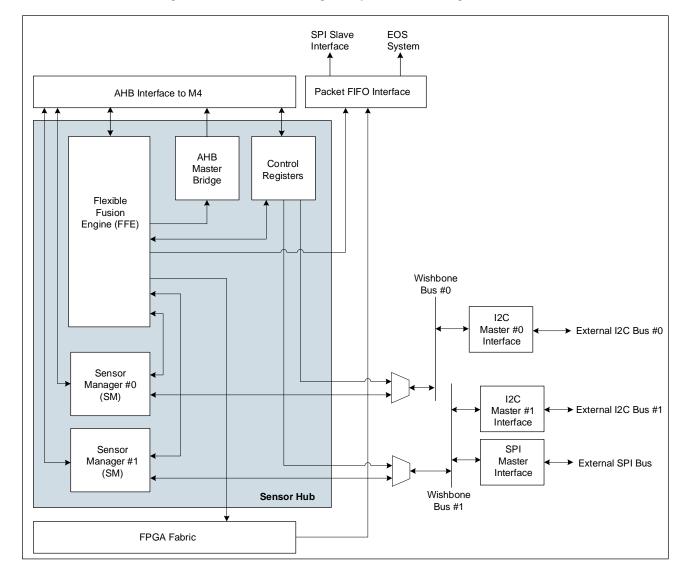

## 1.1. EOS S3 Ultra Low Power multicore MCU Platform Architecture

The following figure shows a system level architecture diagram that highlights the major functional blocks of the EOS S3 Ultra Low Power multicore MCU platform. More detailed block diagrams are provided later in this data sheet that highlights the available datapath options, clock and power domain partitions.

Figure 1: EOS S3 Ultra Low Power multicore MCU Platform Architecture

The following table lists the top-level features. This feature set enables the EOS S3 platform to support use cases in the smartphone and wearable device markets.

Table 1: EOS S3 Platform Supported Features

| Feature                                         | Details                                                                                                                                                                                                                                                                             |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M4-F Subsystem                                  | Cortex M4-F processor with floating point unit support (M4-F) Embedded SRAM (up to 512 KBytes) for code and data memory Vectored interrupt support Wakeup interrupt controller 2-pin SWD port                                                                                       |

| FFE                                             | 50 KB control memory 16 KB data memory Single cycle MAC                                                                                                                                                                                                                             |

| Digital Microphone<br>Support                   | I <sup>2</sup> S microphone PDM microphone On-chip PDM-to-PCM conversion Hardware bypass path for PDM interface to host application processor and/or Voice CODEC Integrated LPSD from Sensory                                                                                       |

| Packet FIFOs Batching<br>Memory                 | 128 KBytes of M4-F SRAM can be used as HiFi sensor batching memory Multiple packet FIFOs to support the FFE to application processor/M4-F data transfers: 8 KBytes packet FIFO with ring-buffer mode support one 256x32 packet FIFO and two 128x32 packet FIFOs                     |

| Power Management Unit                           | Low-power mode with fast wake-up Programmable power modes (deep sleep, sleep with retention, and active) Multiple power domains Power sequencing for sleep and wake-up entry and exit Firmware and hardware-initiated sleep entry Wake-up triggers via internal and external events |

| On-chip Programmable<br>Logic                   | 2,400 effective logic cells with 64 Kbits of RAM, 8 RAM FIFO controllers and 2 GPIO banks Supports SPI Slave configuration Supports reconfiguration from M4-F Supports five clocks                                                                                                  |

| 32 kHz Oscillator with<br>Real-Time Clock (RTC) | 32 kHz crystal oscillator (external crystal required) with bypass option 1 Hz clock generation with compensation register RTC function with one alarm register Start time of 500 ms                                                                                                 |

| High Frequency Clock<br>Source                  | Programmable frequency (2 MHz to 80 MHz) for better frequency resolution Calibrated output (using 32 kHz input) Startup time of 410 µs Clock divider can be programmed in 12 bits                                                                                                   |

| System DMA                                      | 16-channel DMA allows efficient data movement between processing elements                                                                                                                                                                                                           |

| SPI Slave                                       | SPI Slave application processor communication of up to 20 MHz                                                                                                                                                                                                                       |

| Time Stamping                                   | Automatic hardware time stamp on every sensor read in the interrupt mode Up to eight sensor interrupt captured time-stamps (8-bit) Main time stamp of 30 bits for M4-F processor and 24 bits for FFE                                                                                |

|                                                                               | Resolution of 1 msec                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sup>2</sup> C Master and<br>Configurable I <sup>2</sup> C/SPI<br>Interface | I <sup>2</sup> C Master and SPI Master with programmable clock pre-scaler Option to disable multi-master support and slave-inserted wait for shorter SCL cycles Configurable for two I <sup>2</sup> C Masters or one I <sup>2</sup> C Master and one SPI Master                                                                                                                                                                              |

| Other Interfaces                                                              | SPI Master for interfacing with serial flash memories and other external SPI-based peripherals of up to 20 MHz  I <sup>2</sup> S Slave transmitter for downloading audio samples to host application processor                                                                                                                                                                                                                               |

| UART                                                                          | Serial support for M4-F debug and code development Communication with UART-based external peripherals                                                                                                                                                                                                                                                                                                                                        |

| Other Peripherals                                                             | Timers Watchdogs 8-bit GPIO controller                                                                                                                                                                                                                                                                                                                                                                                                       |

| ADC                                                                           | Low sampling rate (12-bit)                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LDO Regulators                                                                | On-chip LDO for system logic Separate on-board LDO for memory                                                                                                                                                                                                                                                                                                                                                                                |

| Integrated Software<br>Debug Interface                                        | 2-pin SWD port for access to the following memory mapped resources: M4-F internal registers and memories FFE and Sensor Manager memories FFE control registers On-chip programmable logic memories On-chip programmable logic designs through generic AHB bus All memory map peripherals such as timers, WDT, SPI Master, etc. I <sup>2</sup> C Master used for I <sup>2</sup> C sensor debug Multiplexed dedicated parallel debug interface |

| Packaging Options                                                             | 42-ball WLCSP (2.66 mm x 2.42 mm x 0.51 mm) (27 user I/Os and 2 VCCIO banks) 64-ball BGA (3.5 mm x 3.5 mm x 0.71 mm) (46 user I/Os and 2 VCCIO banks)                                                                                                                                                                                                                                                                                        |

Note: Not all cores (FFE, eFPGA, LPSD) are available in all devices. Refer to the <u>part numbers table</u> for the correct part number

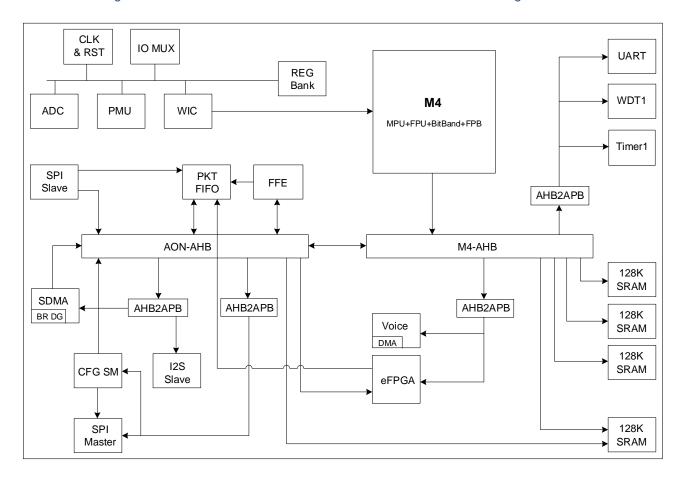

The following figure shows a more detailed view of the datapaths within the EOS S3 Ultra Low Power multicore MCU platform.

Figure 2: EOS S3 Ultra Low Power multicore MCU Platform Block Diagram

### 2. M4-F Processor Subsystem

### 2.1. Subsystem Overview

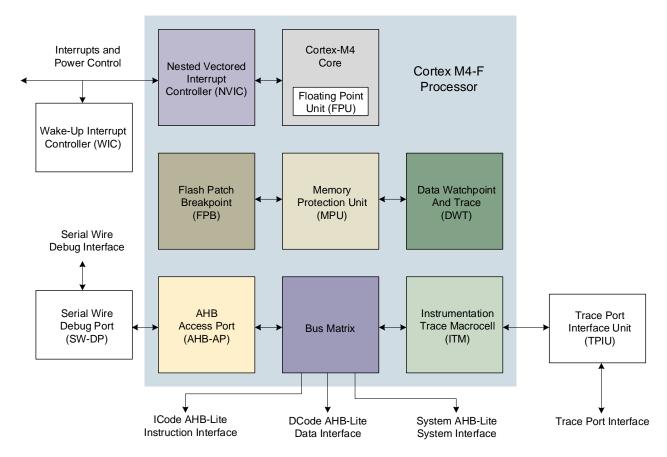

The M4-F 32-bit processor subsystem is one of the primary computation blocks of the EOS platform (shown in the following figure) and includes:

- Optional features such as a Nested Vectored Interrupt Controller (NVIC), flash patch, etc.

- Up to 512 KB SRAM

- Peripheral bus incorporating:

- ② UART

- ② Watchdog Timer

- Imers

Figure 3: Cortex M4-F Block Diagram

The M4-F processor is built on a high-performance processor core, with a 3-stage pipeline Harvard architecture, making it ideal for demanding embedded applications. The processor delivers exceptional power efficiency using an efficient instruction set and extensively optimized design. This combination provides high-end processing hardware that includes optional IEEE754-compliant single-precision floating-point computation, and a range of single-cycle and SIMD multiplication and multiply-with-accumulate capabilities, that ensure saturating arithmetic and dedicated hardware division.

To aid in designing of cost-sensitive devices, the M4-F processor implements tightly-coupled system components that

reduce processor area while significantly improving interrupt handling and system debug capabilities. The M4-F processor implements a version of the Thumb<sup>®</sup>, an instruction set based on Thumb-2 technology, ensuring high code density and reduced program memory requirements. The M4-F instruction set provides the exceptional performance expected of a modern 32-bit architecture, with the high code density of 8-bit and 16-bit microcontrollers.

The M4-F instruction set provides the exceptional performance that is expected of a modern 32-bit architecture, with the high code density of 8-bit and 16-bit microcontrollers. The Cortex M4-F processor closely integrates a configurable NVIC, to deliver industry-leading interrupt performance. The NVIC includes a Non-Maskable Interrupt (NMI) that can provide up to 256 interrupt priority levels.

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to suspend load-multiple and store-multiple operations.

Interrupt handlers do not require wrapping in assembler code, removing any code overhead from the ISRs. A tool-chain optimization also significantly reduces the overhead when switching from one ISR to another. To optimize low-power designs, the NVIC integrates with the sleep modes, which includes an optional deep sleep function. This enables the entire device to be rapidly powered down while still retaining program state.

### 2.1.1. System-Level Interface

The M4-F processor provides multiple interfaces using AMBA® technology to provide high speed, low latency memory accesses. It supports unaligned data accesses and implements atomic bit manipulation that enables faster peripheral controls, system spinlocks and thread-safe Boolean data handling.

The M4-F processor has a Memory Protection Unit (MPU) that permits control of individual regions in memory, enabling applications to utilize multiple privilege levels, separating and protecting code, data and stack on a task-by-task basis.

Such requirements are becoming critical in many embedded applications such as automotive.

### 2.1.2. Integrated Configurable Debug

The M4-F processor can implement a complete hardware debug solution. This provides high system visibility of the processor and memory through a 2-pin SWD port.

For system trace the processor integrates an Instrumentation Trace Macrocell™ (ITM) alongside data watchpoints and a profiling unit. To enable simple and cost-effective profiling of the system events these generate, a Serial Wire Viewer (SWV) can export a stream of software-generated messages, data trace, and profiling information through a single pin.

### 2.1.3. M4-F and Core Peripherals

The M4-F processor provides the following features:

- A low gate count processor core with low latency interrupt processing that includes:

- A subset of the Thumb instruction set, defined in the ARMv7-M Architecture Reference Manual

- Banked Stack Pointer (SP)

- Hardware integer divide instructions, SDIV and UDIV

- Handler and thread modes

- Thumb and debug states

- Support for interruptible-continued instructions LDM, STM, PUSH, and POP for low interrupt latency

- Automatic processor state saving and restoration for low latency Interrupt Service Routine (ISR) entry and

- Support for ARMv6 big-endian byte-invariant or little-endian accesses

- Support for ARMv6 unaligned accesses

©2020 QuickLogic Corporation

- Floating Point Unit (FPU) providing:

- IEEE 754-compliant operations on single-precision, 32-bit, floating point values

- 32-bit instructions for single-precision (C float) data-processing operations

- Combined Multiply and Accumulative instructions for increased precision (Fused MAC)

- Hardware support for denormals and all IEEE rounding modes

- 32 dedicated 32-bit single-precision registers, also addressable as 16 double-word registers

- Decoupled three-stage pipeline

- NVIC closely integrated with the processor core to achieve low-latency interrupt processing

- External interrupts, configurable from 1 to 240

- Bits of priority, configurable from 3 to 8

- Dynamic reprioritization of interrupts

- Priority grouping, enabling selection of preempting and non-preempting interrupt levels

- Support for tail-chaining and late arrival of interrupts, enabling back-to-back interrupt processing without the overhead of state saving and restoration between interrupts

- Processor state automatically saved on interrupt entry, and restored on interrupt exit, with no instruction overhead

- Optional Wake-up Interrupt Controller (WIC), providing ultra-low power sleep mode support

- An optional MPU

- Eight memory regions

- Sub-Region Disable (SRD), enabling efficient use of memory regions

- The ability to enable a background region that implements the default memory map attributes

- Bus interfaces

- Three Advanced High-performance Bus-Lite (AHB-Lite) interfaces: I-Code, D-Code, and System bus interfaces

- Private Peripheral Bus (PPB) based on Advanced Peripheral Bus (APB) interface

- Bit-band support that includes atomic bit-band read and write operations

- Memory access alignment

- Write buffer for buffering of write data

- Exclusive access transfers for multiprocessor systems

- Low-cost debug solution that features:

- Debug access to all memory and registers in the system, including access to memory mapped devices, access to internal core registers when the core is halted, and access to debug control registers even while SYS RSTn is asserted

- Serial Wire Debug Port (SW-DP) debug access

- Flash Patch Breakpoint (FPB) unit for implementing breakpoints and code patches

- Data Watchpoint and Trace (DWT) unit for implementing watchpoints, data tracing, and system profiling

- Instrumentation Trace Macrocell (ITM) for support of printf() style debugging

- Trace Port Interface Unit (TPIU) for bridging to a Trace Port Analyzer (TPA), including Single Wire Output (SWO) mode

#### 2.1.4. Embedded SRAM

The M4-F processor subsystem has up to 512 KB of embedded SRAM that is divided into four sub-blocks of 128 KB each. Each sub-block is accessible simultaneously via four independent AHB busses. Each 128 KB sub-block isfurther divided

down in four 32 KB segments (16 segments in total).

Three of the 128 KB sub-blocks (384 KB) of the SRAM memory reside in the processor power domain. The CPU subsystem must be powered on to access this memory space. Each 128 KB sub-block is addressed as four 32 KB segments (12 segments in total). An interrupt can be triggered when any of the 32 KB memory segments are accessed if the memory is in a lower power state (deep sleep or shut down).

The last 128 KB SRAM sub-block resides in the Always-On power domain and can be accessed regardless of the state of the processor subsystem power.

The 512 KB SRAM can be accessed by the following AHB Masters:

- M4-F system bus

- M4-F I-code bus

- M4-F D-code bus

- Application Processor (AP) through the SPI Slave Interface via the TLC

- Configuration DMA for SPI Flash Controller Master

- Voice DMA

- System DMA

- FFE

The SRAM clocks are dynamically controlled. When there is no activity on the memory, the clocks are gated off to ensure lower power consumption.

### 2.1.5. Development Support (Serial Wire Interface)

Depending on overall EOS S3 platform setup and requirements, two different Serial Wire interfaces can be selected. The external debugger can be connected to either IO\_14/IO\_15 or IO\_44/IO\_45, based on the bootstrap pin IO\_8 (see **Bootstrap Modes**). The two signals are serial wire clock and serial wire data. The optional serial wire viewer can be selected from several different pins.

### 2.1.5.1. Debugger Configuration

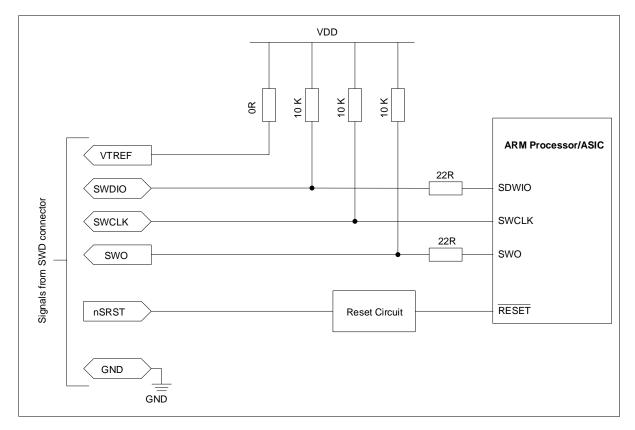

The recommend external configuration if using ARM DS debugger is shown in the following figure. Other debuggers may have different recommendations.

Figure 4: Recommended External Debugger Connection for ARM DS Debugger

### 2.1.6. Debugger Bootstrap Configurations

Upon cold boot up, the M4-F DAP is enabled. The M4-F DBGEN is register-enabled by default and can be disabled later if not needed. The M4-F DAP will only be reset during cold boot up (it is controlled by the POR from APC). The release of the M4-F reset depends on the state of bootstrap pin IO\_19. When it is strapped to high, the M4-F reset is released. When strapped to low, the M4-F reset release depends on AP cfg sm.

- Smartphone/High-Level O/S Wearable Configuration (Application Processor in System)

In a system with an application processor present, the application processor must drive bootstrap pin IO\_19 to indicate whether the Debugger is present. In this configuration, IO\_19 is connected to the application processor as part of the SPI interface (the IO\_19 alternate function is SPIs\_MOSI) and it must drive IO\_19 during the deassertion of SYS\_RSTn. Driving IO\_19 high enables debugger support by releasing the M4-F from system reset

- assertion of SYS\_RSTn. Driving IO\_19 high enables debugger support by releasing the M4-F from system reset immediately. A debugger can take control of the system. Driving IO\_19 low allows the system to boot normally, which disallows the debugger access until after M4-F is released from reset. Once the M4-F is booted, the debugger can be attached.

- Wearable Configuration (EOS S3 platform operating as Host)

- In a wearable design, bootstrap pin IO\_19 must always be strapped low to allow M4-F operation. Once the boot code is downloaded and the M4-F is released from reset, the debugger can be attached to the system.

### 3. Sensor Processing Subsystem

### 3.1. Overview

The Sensor Processing Subsystem provides the EOS S3 device with the ability to perform sensor fusion operations while using low overall power. The following figure illustrates the architecture of this module.

Figure 5: Sensor Processing Subsystem Block Diagram

The key to the Sensor Processing Subsystem is the FFE. This block is responsible for coordinating the retrieval of sensor data by each Sensor Manager and using this data for sensor fusion operations.

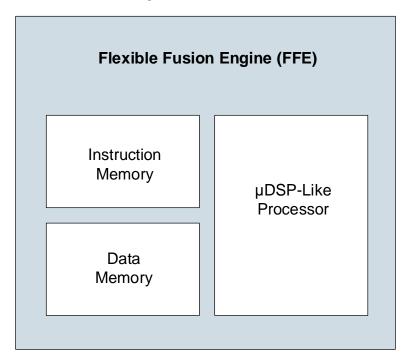

### 3.2. Flexible Fusion Engine

The FFE is responsible for the following:

- Coordinating the operation of the Sensor Manager(s)

- Retrieval of sensor data retrieved by the Sensor Manager(s)

- Sensor fusion calculations

- Transferring the results of the sensor fusion calculations to the EOS S3 platform

- Coordinating FFE operations with on-chip programmable logic IP. The following figure illustrates the features

of the FFE architecture.

Figure 6: FFE Architecture

The FFE consists of three basic blocks:

- DSP-Like Processor

- Instruction Memory

- Data Memory

### 3.2.1. µDSP-Like Processor

The  $\mu$ DSP provides the main operation of the FFE. The  $\mu$ DSP retrieves instructions from the Instruction Memory along with data values stored in the Data Memory. In addition, the  $\mu$ DSP performs the following selected operations:

- Waiting for a Start signal from the EOS S3 platform to begin processing

- Receiving Mailbox values from the EOS S3 platform to direct FFE processing

- Writing Mailbox values to the Sensor Manager Memory. The Mailbox values determine which sensors will be contacted by the Sensor Manager during each sampling period.

- Reading sensor data values from the Sensor Manager Memory prior to starting a new Sensor Manager session.

- Starting each Sensor Manager session to retrieve a new set of sensor data

- In parallel with the Sensor Manager session, performing Sensor Fusion calculations based on the sensor data

values retrieved from Sensor Manager Memory.

- Sending the results of the Sensor Fusion calculations to the EOSS3 platform. The FFE can use either the Packet FIFO interface or the AHB Master port to pass packets of sensor data to the EOSS3 platform

- Coordinating FFE operations with on-chip programmable logic-based IP. This IP waits for a Start signal from the EOS S3 system prior to beginning processing.

### 3.2.2. Instruction Memory

The Instruction Memory contains the instructions used by the  $\mu$ DSP for performing the Sensor Fusion operation. The EOS S3 platform loads this memory prior to the beginning of the first FFE session. At the start of each session,  $\mu$ DSPs reading instructions from this memory staring at address 0 and continuing until a Stop instruction is read.

The EOS S3 platform may elect to alter the Sensor Fusion operation on a session-by-session basis by passing Mailbox data from the Control Registers module. If the EOS S3 platform does this, it does not need to modify the Instruction or Data Memories to support multiple Sensor Fusion processing modes. It is important to note that the FFE cannot write to its own Instruction Memory. Similarly, no other module within the Sensor Processing Subsystem can read or write to the Instruction Memory.

### 3.2.3. Data Memory

The Data Memory contains the data portion of the µDSP program execution. The EOS S3 platform loads this memory prior to the beginning of the first FFE session. The Instruction Memory determines which portions of Data Memory the Microcontroller reads or writes thereafter. Values stored in Data Memory can include:

- Constant values

- Variable values

- Sensor data values

It is important to note that both the EOS S3 platform and FFE can write to this memory. However, this does not extend to any other module in the Sensor Processing Subsystem.

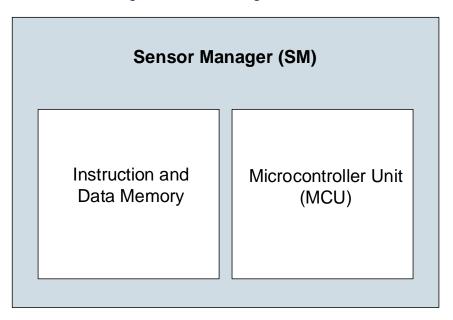

### 3.3. Sensor Manager

The Sensor Manager is responsible for the following tasks:

- Coordinating its actions with the FFE.

- Using the Wishbone bus interface to access the I2C/SPI Master modules.

- Managing external sensors:

- Sensor data retrieval (such as single values, burst transfers, FIFO transfers, etc.)

- Sensor configuration

- Sensor calibration

- Sensor power state management

- Storing sensor data in the proper format for retrieval by the FFE.

The following figure illustrates the features of the Sensor Manager architecture.

Figure 7: Sensor Manager Architecture

The Sensor Manager consists of two parts:

- Microcontroller Unit

- Instruction and Data Memory

### 3.3.1. Microcontroller Unit

The Microcontroller Unit (MCU) is responsible for the operation of the Sensor Manager. The MCU retrieves instructions and data from its memory module and performs operations that include:

- Reading the Mailbox data written by the FFE. The Mailbox data defines which sensor handling routines to execute during the current Sensor Manager session.

- Executing the selected sensor handling routines.

- Accessing the target sensor through the appropriate I<sup>2</sup>C Master or SPI Master interface.

- Storing sensor data in the appropriate packet format for retrieval by the FFE.

It is important to note that each Sensor Manager session is not necessarily targeted at sensor data retrieval. As mentioned earlier, some sessions may be targeted at configuring sensors, or changing power state. The FFE selects which sensor operations will be active during each Sensor Manager session. Additionally, the Sensor Manager focuses on sensor management. As such, it does not participate in Sensor Fusion calculations.

### 3.3.2. Instruction and Data Memory

The Instruction and Data Memory holds the information that the Microcontroller uses for each of its processing sessions. Prior to the first processing session, the EOS S3 platform (e.g., M4-F or application processor) loads this memory with a series of sensor management routines. The algorithms loaded into the FFE determine, on a session by session basis, which of these routines the Sensor Manager will use. More specifically, the FFE algorithms write to a Mailbox data structure in the Sensor Manager memory. In response, the Sensor Manager only uses those routines enabled for the current session. The purpose for this approach is to enable the Sensor Manager to sample each sensor at its own rate.

The Sensor Manager stores the retrieved sensor data into the Instruction and Data Memory. The location and format of the resulting data structure helps the FFE to correctly retrieve and process this data. The format of the data structure is not fixed by hardware. Rather, it is left to software to define and implement this structure as needed.

### 3.4. I<sup>2</sup>C Master

There are two  $I^2C$  Master modules in the EOS S3 device, and each one is assigned to a Sensor Manager module. The EOS S3 platform also makes both of these  $I^2C$  Master modules directly accessible to the EOS S3 platform internal bus system. In each case, the  $I^2C$  Master module provides the means for accessing devices on the associated  $I^2C$  bus.

AHB Interface to M4 Control Wishbone Registers **Sensor Processing** Bus #0 Subsystem (Simplified) I2C Master #0 External I2C Bus #0 Interface Sensor Manager #0 (SM) I2C Master #1 ➤ External I2C Bus #1 Interface SPI Sensor Manager #1 Master External SPI Bus (SM) Interface Wishbone Bus #1

Figure 8: I2C Modules within the EOS S3 Platform

The I<sup>2</sup>C is a two-wire, bi-directional serial bus that provides a simple and efficient method of data exchange between devices. It is most suitable for applications that require occasional communication over a short distance between many devices.

The  $I^2C$  standard is a true multi-master bus that includes collision detection and arbitration to prevent data corruption if two or more masters attempt to control the bus simultaneously.

The interface defines three transmission speeds:

Normal: 100 KbpsFast: 400 Kbps

High speed: 3.5 Mbps

Only 100 Kbps (Normal) and 400 Kbps (Fast) modes are directly supported. The following features are available in the I<sup>2</sup>C Master block:

- Compatible with the Philips I<sup>2</sup>C standard

- Multi-master operation

- Software-programmable clock frequency

- Clock stretching and wait state generation

- Software programmable acknowledge bit

- Interrupt or bit-polling driven byte-by-byte data-transfers

- Arbitration lost interrupt, with automatic transfer cancellation

- Start/Stop/Repeated Start/Acknowledge generation

- Start/Stop/Repeated Start detection

- Bus busy detection

- Supports 7-bit and 10-bit addressing mode

- Operates from a wide range of input clock frequencies

- Static synchronous design

- Fully synthesizable

The following sections describe the I<sup>2</sup>C system operations.

### 3.4.1. System Configuration

The I<sup>2</sup>C system uses a serial data line (SDA) and a serial clock line (SCL) for data transfers. All devices connected to these two signals must have open drain or open collector outputs. The logic AND function is exercised on both lines with external pull-up resistors.

Data is transferred between a Master and a Slave synchronously to SCL on the SDA line on a byte-by-byte basis, and each data byte is 8 bits long. There is one SCL clock pulse for each data bit with the MSB being transmitted first. An acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; as a result, the SDA line can be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (for details, see **START Signal** and **STOP Signal**).

### 3.4.2. I<sup>2</sup>C Protocol

Normally, standard communication consists of the following four parts:

- START signal generation

- Slave address transfer

- Data transfer

- STOP signal generation

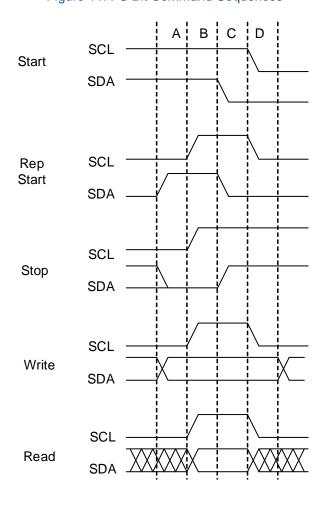

The following figure illustrates an example of I<sup>2</sup>C protocol.

Figure 9: I<sup>2</sup>C Protocol Example

### 3.4.3. START Signal

When the bus is free/idle, this means no master device is engaging it (and both SCL and SDA lines are high), and the master can initiate a transfer by sending a START signal. A START signal, usually referred to as the S-bit, is defined as a high-to-low transition of SDA while SCL is high. The START signal denotes the beginning of a new data transfer.

A Repeated START is a START signal that is sent without first generating a STOP signal. The master uses this method to communicate with another slave or with the same slave in a different transfer direction (for example, changing from writing to a device to reading from a device) without releasing the bus.

The core generates a START signal when the STA-bit in the Command Register is set and the RD or WR bits are set.

Depending on the current SCL line status, it generates a START or Repeated START.

#### 3.4.4. Slave Address Transfer

The first byte of data transferred by the master immediately after the START signal is the slave address. This is a 7-bit calling address followed by a RW bit. The RW bit signals to the slave the data transfer direction. No two slaves in the system can have the same address.

Only the slave with an address that matches the one transmitted by the master responds by returning an acknowledge bit, which pulls SDA low at the ninth SCL clock cycle.

**NOTE:** The core supports 10-bit slave addresses by generating two address transfers. For details, see the Philips I<sup>2</sup>C specifications.

The core treats a Slave address transfer like any other write action. The core stores the slave device address in the Transmit Register, sets the WR bit and then transfers the slave address on the bus.

#### 3.4.5. Data Transfer

Once successful slave addressing has been achieved, the data transfer can proceed on a byte-by-byte basis in the direction specified by the RW bit sent by the master. Each transferred byte is followed by an acknowledge bit on the ninth SCL clock cycle. If the slave signals a No Acknowledge, the master can generate a STOP signal to abort the data transfer or generate a Repeated START signal and start a new transfer cycle. If the master, as the receiving device, does not acknowledge the slave, the slave releases the SDA line for the master to generate a STOP or Repeated START signal.

To write data to a slave, store the data to be transmitted in the Transmit Register and set the WR bit. To read data from a slave, set the RD bit. During a transfer, the core sets the TIP flag, indicating that a transfer is in progress. When the transfer is done, the TIP flag is reset, the IF flag is set, and when enabled, an interrupt is generated. The Receive Register contains valid data after the IF flag has been set. The user can issue a new write or read command when the TIP flag is reset.

### 3.4.6. STOP Signal

The master can terminate the communication by generating a STOP signal. A STOP signal, usually referred to as the P-bit, is defined as a low-to-high transition of SDA while SCL is at logical 1.

### 3.4.7. Arbitration

The I<sup>2</sup>C Master block supports multi-master arbitration. However, this feature is not supported by other elements of the EOS S3 platform.

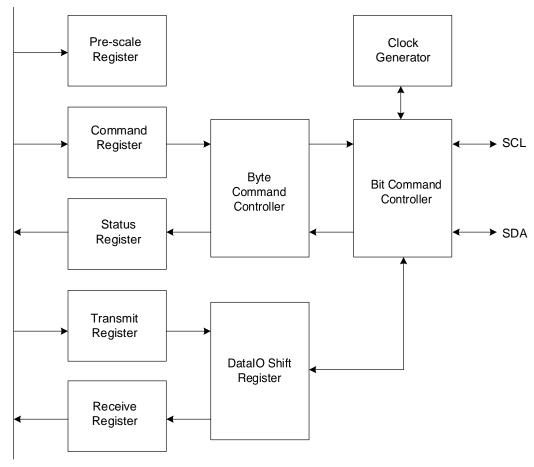

#### 3.4.8. I<sup>2</sup>C Core Architecture

The I<sup>2</sup>C core is built around the following four primary blocks (as shown in the following figure):

- Clock Generator

- Byte Command Controller

- Bit Command Controller

- DataIO Shift Register.

NOTE: All other blocks are involved with interfacing or for storing temporary values.

Figure 10: I2C Block Diagram

Wishbone Interface

The Sensor Manager uses the Wishbone interface to access the I<sup>2</sup>C Master during sensor data transfers.

#### 3.4.9. Clock Generator

The Clock Generator generates an internal 4\*Fscl clock enable signal that triggers all of the synchronous elements in the Bit Command Controller. In addition, it also handles clock stretching required by some slaves.

### 3.4.10. Byte Command Controller

The Byte Command Controller handles I<sup>2</sup>C traffic at the byte level. It takes data from the Command Register and translates it into sequences based on the transmission of a single byte. By setting the START, STOP, and READ bit in the Command Register, the Byte Command Controller performs the following sequence:

- A START signal is generated

- The byte is read from the slave device

- A STOP signal is generated

Setting the START, STOP, and READ bits and the Byte Command Controller sequence starts a process that acts to divide each byte operation into separate bit-operations, which are then sent to the Bit Command Controller.

#### 3.4.11. Bit Command Controller

The Bit Command Controller handles the actual transmission of data and the generation of the specific levels for START, Repeated START, and STOP signals by controlling the SCL and SDA lines.

The Byte Command Controller tells the Bit Command Controller which operation needs to be performed. For a single-byte read, the Bit Command Controller receives eight separate read commands. Each bit-operation is divided into five smaller pieces (idle and A, B, C, and D), except for a STOP operation which is divided into four smaller pieces (idle and A, B, and C). The following figure illustrates the I<sup>2</sup>C bit command sequences.

Figure 11: I<sup>2</sup>C Bit Command Sequences

### 3.4.12. Data I/O Shift Register

The DatalO Shift Register contains the data associated with the current transfer. During a read action, data is shifted in from the SDA line. After a byte has been read, the contents are copied into the Receive Register. During a write action, the contents of the Transmit Register are copied into the DatalO Shift Register and are then transmitted onto the SDA line.

### 3.5. Serial Peripheral Interface (SPI)

The EOS S3 platform relies on three separate SPI interfaces.

- SPI Master for System Support

- SPI Master for Sensor Subsystem Support

SPI Slave

The following sections describe each of these interfaces.

### 3.5.1. SPI Master for System Support

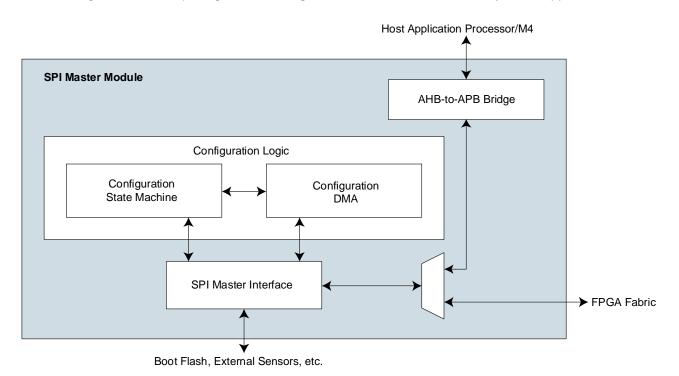

IP within the on-chip programmable logic can directly access the SPI Master for system support interface. The following figure shows this connection.

Figure 12: On-Chip Programmable Logic IP Access to SPI Master for System Support

The ability to directly access the SPI Master provides an IP designer with the option to create on-chip programmable logic IP that can directly access external devices such as Flash Memory or Sensors. In the latter case, the Sensor data values can be used for additional Sensor Fusion operations in parallel with the Sensor Processing Subsystem. In such cases, the on-chip programmable logic IP can use either the Packet FIFO Interface or use the SDMA to move the processed data into the EOS S3 platform for further evaluation or processing.

During the initial boot operation, the SPI Master is exclusively accessed by the Configuration Logic. Once the Configuration Logic completes the initial boot operation, the SPI Master becomes available to the M4-F for additional data retrieval from the external flash device. More specifically, the initial boot code provides a boot loader to the M4-F for the M4-F to complete its retrieval of M4-F code.

After the boot process is completed, either the M4-F or on-chip programmable logic can access the SPI Master Interface and use this to access any device on the SPI bus. This can be additional external flash devices, sensors, or system support devices such as Power Management devices.

### 3.5.2. SPI Master for System Support Features

The SPI Master interface supports the following operations:

- Single SPI transfers

- DMA transfers of SPI data retrieved from an external flash device. The following features show the operation

of this module.

- SPI Master Interface provides the following:

- Operates as a Master only

- Supports up to three slaves

- Operates in mode 0 (this can be reprogrammed by M4)

- Supports a frame size of 8 (this can be reprogrammed by M4)

- Supports a maximum transfer size of 64K frames

- Supports little-endian data ordering

- Shifts out the most significant bit data first

- Supports DMA transfers

- Supports standard SPI protocol

- SPI Master Interface does not provide the following:

- Support for multiple SPI masters

- Support for other serial protocols (such as SSP or Microwire)

- Support for protocols that include DDR, dual, and guad transfers

- SPI Master Interface that is accessible by:

- Host Application Processor

- Configuration Logic

- On-chip programmable logic

- Configuration Logic is responsible for:

- Reading the external flash device

- Configuring its SPI transfer parameters using data stored within the external flash devices

- Confirming that the boot code is compatible with the EOS S3 device using stored values in the external flash

- Loading the boot code into M4-F memory and enabling the M4-F execution once the boot code transfer has completed

- Minimizing the elapsed time for booting the M4-F by using DMA transfers of boot code from the external flash

- Posting status bits to the M4-F that aid in diagnosing the state of the boot process

### 3.5.3. Configuration Logic

The configuration logic consists of the following two parts:

- Configuration State Machine

- Configuration DMA logic

The Configuration State Machine provides control over retrieving boot code from an external flash device. To complete this operation, the Configuration State Machine must configure and control the Configuration DMA and SPI Master Interface.

The Configuration State machine programs the Configuration DMA and SPI Master Interface to access an external flash, by performing the following operations:

- Setting the correct SPI clock rate

- Awakening the external Flash device from a low power state (such as a deep sleep modes)

- Examining the boot code parameters to optimize SPI Master transfers

- Initiating DMA loading of the M4-F boot code into M4-F memory

- Enabling M4-F operations

As a part of this process, the Configuration State Machine examines the EOS S3 device ID in the boot flash data. If this device ID is incorrect, the Configuration State Machine halts the boot process, and this boot process can only be restarted by asserting a reset.

### 3.5.4. SPI Master for Sensor Processing Subsystem Support

The EOS S3 platform SPI Host Controller can communicate with up to eight SPI sensor devices using the Wishbone classic interface.

The SPI Master Interface features include:

- Support for Master configuration (multi-master configuration is not supported)

- Connection capability supports up to eight SPI slaves with individual slave select lines

- Interrupt generation capability

- Serial clock with programmable phase and polarity

- Four programmable transfer formats supported (controlled by CPOL and CPHA)

- Support for all current SM instructions

- Support all operations (identical to the I<sup>2</sup>C Master Controller)

- 8-bit Wishbone interface (identical to the I<sup>2</sup>C Master Controller)

The SPI Master module used for the Sensor Processing Subsystem support resides on the same Wishbone bus as the I<sup>2</sup>C Master module described in **Sensor Manager** and **Control Registers**. Similar to the I<sup>2</sup>C Master module, the SPI Master module enables the Sensor Processing subsystem to communicate with external devices.

The SPI module is accessible to the M4-F processor but is not used for operations such as retrieving boot code from external flash storage devices. The operation is left to the SPI Master used for System Support.

The following figure shows the basic connections to the SPI Interface that supports the Sensor Processing subsystem.

Sensor Hub (Simplified)

Control Registers

Sensor Manager #1 (SM)

Sensor Manager #1 (SM)

Wishbone Bus #1

Figure 13: SPI Interface used for Sensor Processing Subsystem Support

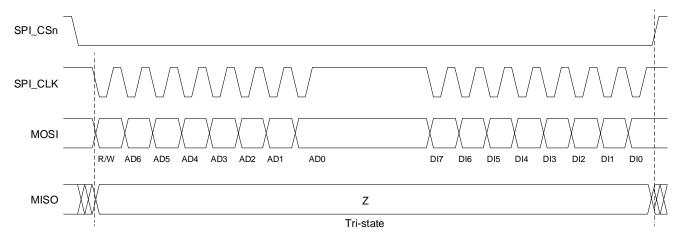

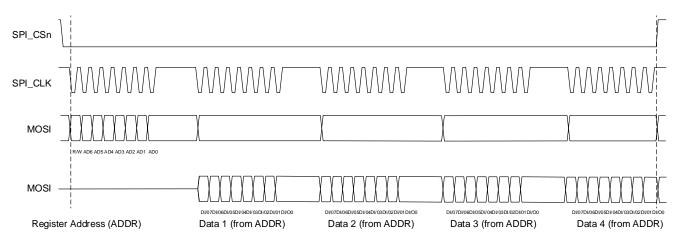

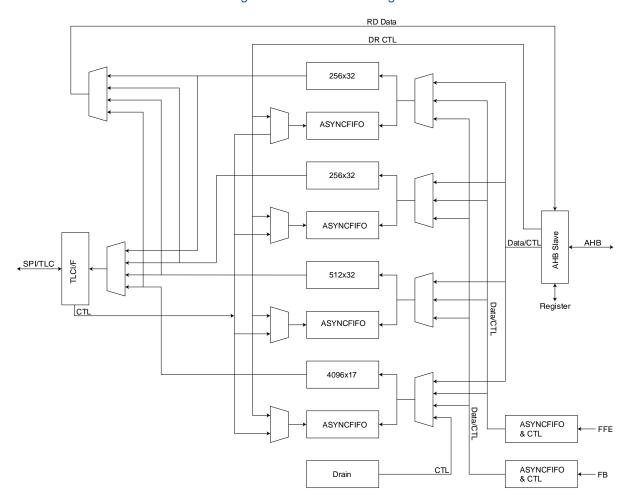

### 3.5.5. SPI Slave

The SPI Slave module provides the means for communicating between a host system and the EOS S3 platform. This block consists of the SPI Interface and the Top Level Controller (TLC) module.

The SPI Slave module performs the following two roles:

- Setting up and debugging the EOS S3 platform

- Retrieving run-time data

Both of these operations are possible during either *Smart Phone* or *Wearable* EOS S3 modes. However, in a typical *Wearable* application, there is no local Host to use the SPI Slave interface. Therefore, the following description is primarily focused on the *Smart Phone* mode of operation.

During the EOS S3 platform non-debug setup operations, the Host system uses the SPI Slave module to write a precompiled binary file to the EOS S3 device M4-F memory. In addition, the Host also writes precompiled binary files to other memories such as those used by the FFE and the Sensor Manager. After completion, the Host system enables the EOS S3 platform M4-F processor to execute the newly written binary code.