クイックロジックは、FPGA、FPGA SoC、eFPGA IP コアの設計において 30 年以上の実績を誇ります。これらのコアは、オープンソースのレイアウト自動生成技術をベースに開発した独自のツール、およびオープンソースの FPGA ユーザー ツールでサポートされています。

サポート

多様なファウンドリ/プロセス ノードに対応

タイムフレーム

カスタム GDSII をわずか数日間で作成

低コスト

従来型 eFPGA IP コアの数分の一

統合

多様な IP の統合と FPGA ユーザー ツール サポート

クイックロジックの IP ジェネレーター ツール「Australis」、および複数の FPGA ユーザーツールでサポートされています。

Australis とは?

Australis は、OpenFPGA プロジェクトのシリコン自動設計技術をベースにクイックロジックがこれまで 30 年間積み上げたプログラマブル ロジック アーキテクチャの設計知識を集結させて完成した eFPGA IP ジェネレーター ツールです。シリコン効率に優れた高品質で信頼性の高いデザインを生成し、マスカスタマイゼーションにも対応できます。

利点

- 市場投入までの期間を短縮 -迅速な開発をサポートするカスタマイズ済み eFPGA IP

- SoC 設計要件に柔軟に対応 - 消費電力、性能、エリアなどの要件に最適化

- コスト効率が良い - 作業の自動化によってコストと時間を大幅に削減できるため、要件を満たしたコアを低コストでカスタマイズ可能

機能

- eFPGA IPは任意のファウンドリとプロセス技術に合わせて生成およびカスタマイズ可能。すでに対応しているプロセス ノードは数日程度、新しいプロセス ノードでも 3 カ月以内

- eFPGA は性能、消費電力、エリアに最適化可能

- 多様な eFPGAアーキテクチャ (LUT4 ~ LUT6)、多様な配線密度

- 多様な eFPGAアレイ サイズに対応。オプションでブロック RAM や DSP ブロックを統合できる

リソース

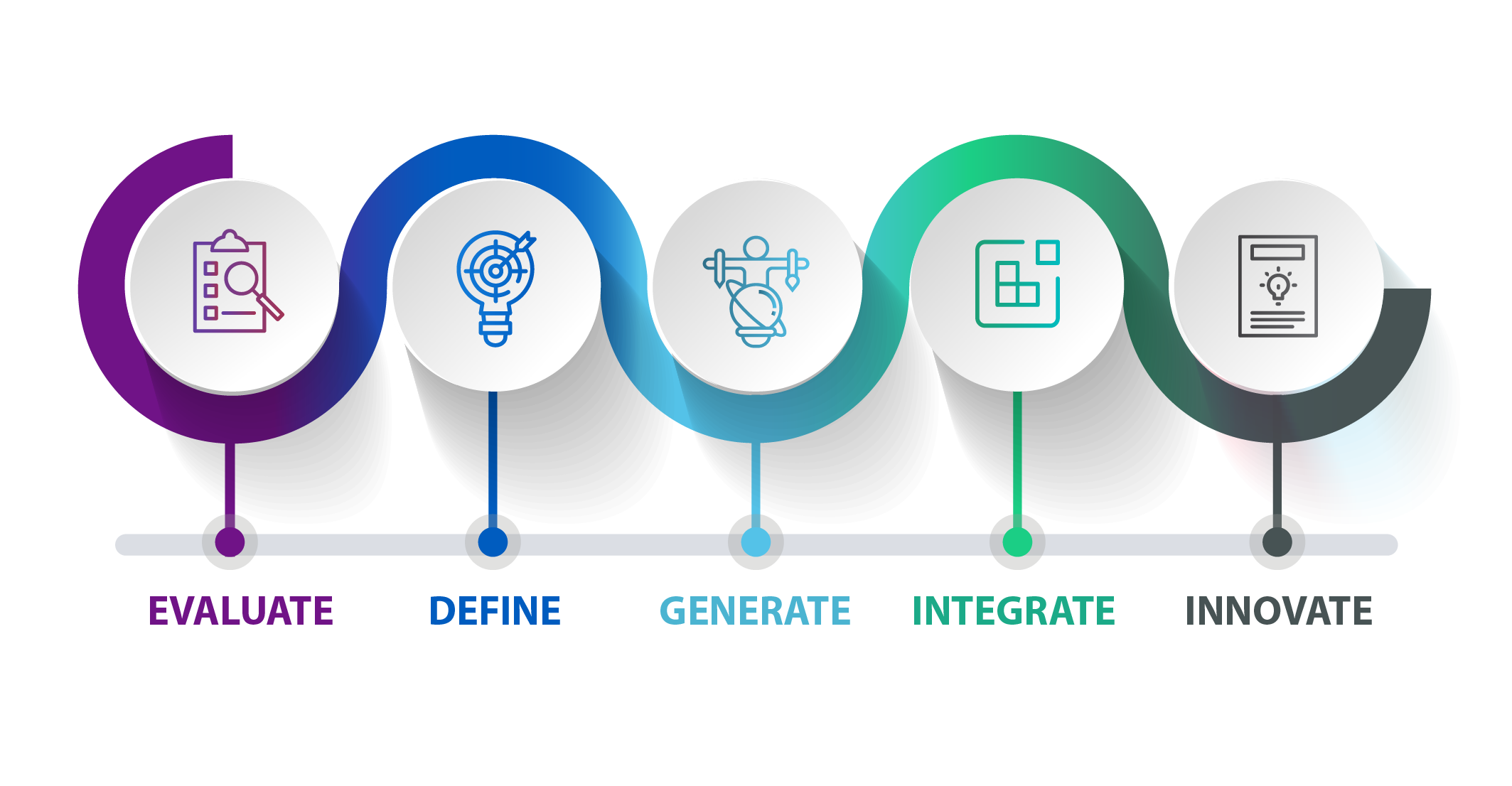

eFPGA IP 2.0 開発フロー

ニーズが多様化し、マスカスタマイゼーションの重要性が高まっています。すべてのユーザーに同じコアを提供するのではなく、ニーズに合ったコスト効率の良い eFPGA コアと FPGA ユーザー ツールを提供することが求められているのです。クイックロジックの開発フローは、各要件に合った最適なコア生成をサポートするツールを提供し、すべてのプロジェクトを成功に導きます。

eFPGA ユーザー ツール

クイックロジックの QORC (QuickLogic Open Reconfigurable Computing) イニシアチブは、プログラマブル ロジックという枠組みを再定義し、オープンソースを活用する開発環境を 21世紀にもたらしました。FPGA/eFPGA ユーザー ツールとして、完全オープンソースの SymbiFlow とオープンソース ツールをベースにクイックロジックが独自開発した Aurora ツールを提供しています。

詳細従来型のシリコン検証済み IP コア

| プロセス | |||||||||

| 0.25 um | 180 nm | 130nm | 90nm | 65nm | 40nm | 28nm | 22nm | 12nm | ||

ファウンドリ パートナー

アプリケーション

防衛

航空宇宙

産業

オーディオ/ビデオ

医療