eFPGA User Tools

The Aurora 2.6 Development Tool Suite integrates fully open-source modules for scalability, longevity, and full code transparency.

Contact Us to Start your EvaluationThe Aurora 2.6 Development Tool Suite integrates fully open-source modules for scalability, longevity, and full code transparency.

Contact Us to Start your EvaluationAurora is now available on Windows 11/Windows 10 OS platform and all of the major Linux distributions (including Centos, RedHat, and Ubuntu), via a unified Linux installation package.

The Aurora 2.6 suite brings an improved K6N10 architecture, delivering an average timing performance boost of 6% across various designs. In certain cases, the enhancement leaps to as much as 15%, underscoring QuickLogic's dedication to optimizing performance and efficiency. Detailed comparisons and benchmarks are available for review, showcasing the tangible benefits of the updates implemented in this version.

A standout addition is the Interactive Path Analysis (IPA) within the new Graphical User Interface (GUI). Interactive Path Analysis (IPA) Feature allows users to debug their design timing in lot more detail by highlighting the routing for critical paths in the design. This will enable users to decide how they can improve the design's timing performance. The inclusion of IPA exemplifies Aurora's evolution towards more intuitive and insightful design analysis, facilitating smoother development processes for engineers.

Aurora's Inferencing feature streamlines the implementation of reconfigurable computing algorithms, by automatically adapting BlockRAM (BRAM) read/write widths, eliminating the need for manual RTL design modifications.

The Single Stage Routing algorithm significantly enhances the maximum operating frequency (Fmax) of designs for QuickLogic eFPGA cores. It has shown an impressive Fmax increase of up to 24% in QuickLogic's benchmark designs, ultimately optimizing FPGA performance.

This latest version of the Aurora FPGA Tools calculates dynamic power from a user’s design’s clock frequencies and extracted capacitance models extracted from QuickLogic’s ASIC-like design methodology.

The Tools simplify power calculation for eFPGA cores by automatically estimating dynamic power consumption based on design clock frequencies and capacitance models. This automation, coupled with QuickLogic's CI infrastructure and CLI options, enables users to efficiently calculate power consumption across a range of designs.

Time Efficiency: It significantly reduces the time-consuming task of understanding dynamic power consumption across a wide range of use cases, making it more efficient for users.

Reproducibility: The feature calculates dynamic power based on design clock frequencies and capacitance models, ensuring consistent and reliable power estimates.

Automation: With QuickLogic’s Continuous Integration (CI) infrastructure, Command Line Interface (CLI) option, and advanced scripting examples, FPGA users can calculate anticipated power consumption across libraries of user designs – in a fully automated way.

Flexibility: The feature is adaptable to a variety of user designs, enhancing its versatility for different applications and scenarios.

The tools includes several developments to the workflow to improve overall user’s design time. These include:

With QuickLogic’s Australis eFPGA IP Generator, and the evaluation results from running Aurora, customers can customize and specify the architecture without being restricted to a pre-defined fixed tile implementation.

Modifications include:

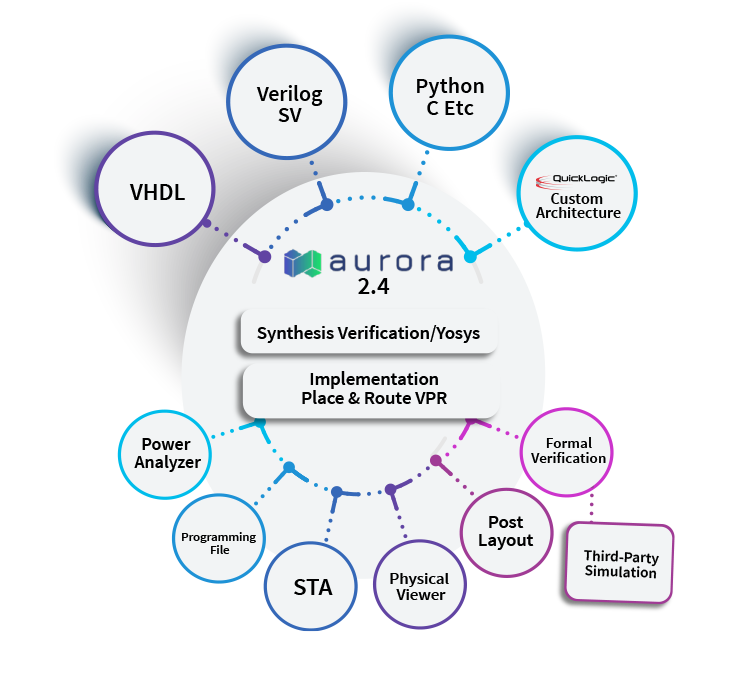

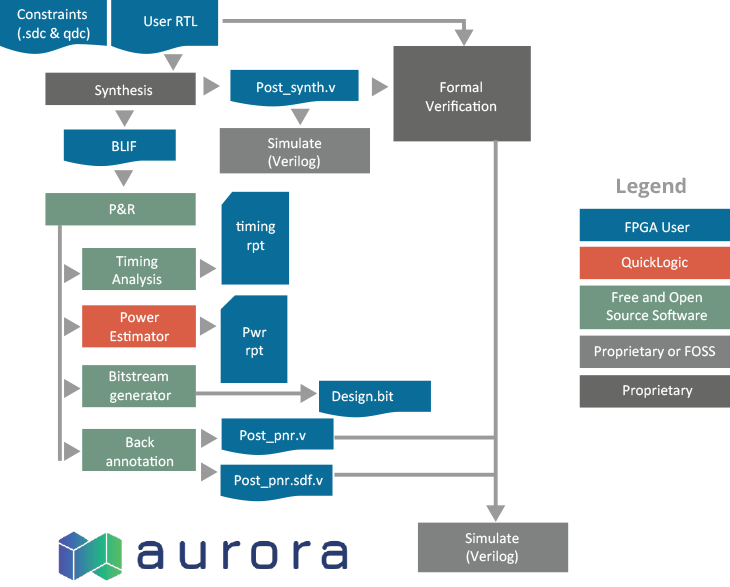

The Aurora 2.4 Development Tool Suite is based on fully open-source implementation for scalability, longevity, and full code transparency. It supports all major development languages including Verilog, System Verilog and VHDL. Aurora uses open-source synthesis tool (Yosys) for front end synthesis. There are custom plugins developed in Yosys to efficiently target QuickLogic eFPGA architecture features and achieve the best Quality of Result (QoR). The synthesis tool uses ABC engine for logic-optimization and technology mapping which supports both area and delay trade-off.

The netlist generated by the synthesis tool is available within Aurora to run the implementation flow. The Implementation flow within Aurora uses open-source Versatile Place & Route (VPR) Tool for Packing, Placement and Routing. The Implementation flow support area vs speed tradeoff by implementing Timing Driving algorithms and supports specifying SDC (Syopsys Design constraint) to achieve best Quality of results (QoR). The placement engine also uses Reinforcement Learning (RL) techniques to achieve the best run-time without sacrificing the QoR.

Aurora tool reports detailed design resource utilization after each stage of the Implementation flow to help end-user understand the how effectively the design is mapped to the FPGA resources.

Aurora’s Static Timing Analysis engine provides Timing Summary of the designs by providing key timing metrics like Fmax, Critical path delay (CPD), Worst Negative Slack (WNS), Total Negative Slack (TNS) and Slack Histogram. STA also provides detailed setup and hold timing violations report to allow easy debugging of the critical paths in the designs.

eFPGA cores have nearly unlimited reprogrammability, therefore, understanding dynamic power consumption across the universe of use cases can be an incredibly time-consuming task. This latest version of the Aurora FPGA Tools calculates dynamic power from a user’s design’s clock frequencies and extracted capacitance models extracted from QuickLogic’s ASIC-like design methodology. Moreover, with QuickLogic’s Continuous Integration (CI) infrastructure, Command Line Interface (CLI) option, and advanced scripting examples, FPGA users can calculate anticipated power consumption across libraries of user designs – in a fully automated way.

Aurora tool generates the post-layout files (Verilog and SDF) after the Placement & Routing. The post layout Verilog file along with the timing annotation can be used along with Quicklogic provided primitive libraries to verify the functionality and timing of the design using any industry-standard simulator such as Questa, Active-HDL, NC-Sim, and VCS, or other open-source simulators.

Aurora’s enhanced IDE (Integrated Development Environment) based makes it easy for designers to Import their user designs into the too, run through the complete execution flow, generate detailed metrics, debug and gain a better understanding about the design and its placement, routability, and more. Aurora’s built-in Physical Viewer provides ease-of-use options to the eFPGA user, which makes it easier to understand how the design is being mapped to the eFPGA fabric.